Диодный дешифратор адресной выборки

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИЯИТВЛЬСТВУ

Союз Советских

Социалистимеских

Республик (11) 47 843 8 (61) Дополнительное к авт, свид-ву (22) Заявлено 31.08.70 (21) 1472 337/18-24 (51) М. Кл.

Н 03к 13/252 с присоединением заявки №вЂ”

Государственный комитет

Совета Министров СССР ео делам иэаеретений и открытий (23) Приоритет(43) Опубликовано 25.07.75.Бюллетень №27 (53) УДК 681.325.53 (088.8 ) (45) Дата опубликования описания 20.06.75 (72} Авторы изобретения

А. Е. Ашман, В. А. Кнох и М. С. Любчанский (71) Заявитель (54) ДИОДНЫЙ ДЕШИФРАТОР АДРЕСНОЙ ВЫБОРКИ

l.

Изобретение относится к вычислитель- ) ной технике и предназначено для исполь зования в качестве дешифратора адреса в системах выборки информации, например, в запоминаюших устройствах на магнитных элементах.

Известны дешифраторы адресной выборки в запоминаюших устройствах на магнитных элементах:, в которых в выходной ступени применяются диоды.

Однако практическое построение таких устройств связано в ряде случаев со значительными трудностями ввиду отсутствия диодов с требуемыми параметрами по допустимым токам и мощностям рассеивания, а также с дополнительными трудностями обеспечения необходимой стабильности токов управления при значениях этих токов, близких к предельным для используемых диодов.

Предложенный дешифратор адресной выборки допускает использование диодов (диодных сборок) с предельно-допустимыми токами меньшими, чем требуемые токи управления в устройстве, позволяя при этом обеспечить высокую надежность ра- " боты диодов (сборки) и одновременно обеспечивает минимум элементов в схемах самого дешифратора адреса.

Цель изобретения- упрошение устройства и повышение его надежности.

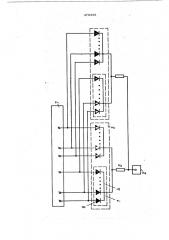

В предлагаемом устройстве первые электроды всех диодных сборок каждой группы объединены и подключены через

10 выравниваюший резистор к соответствуюшему формирователю, вторые электроды вЂ,х диодов К вЂ” х диодных сборок всех групп объединены и соединены с (t,- К )-й шиной выборки накопителя.

15 На чертеже изображена схема устройства.

Диодные сборки 1, подключаемые к каждому из формирователей тока 2, разделены на группы 3. Обшие выводы 4 диод20 ных сборок 1 в группе 3 обьединены и .через выравниваюшие. резисторы 5 подклю чены к формирователю тока 2. Вторые

Ф выводы g -х диодов 6 К -. .х диодных сборок 1 из всех групп 3 объединены по

25 одному диоду из каждой группы сборок и

478438

3 соединены с соответствующей (— К ) -й шиной 7 выборки накопителя.

В предлагаемом устройстве есть возможность существенно расширить диапазон управляющих токов, что особенно важно для 5 устройств, в которых применяются запоми- нающие элементы с незамкнутой областью работоспособности и работающих в широком температурном интервале. Это позволяет резко повысить надежность работы запоми- 10 наюших устройств как из-за расширания области надежной работы элементов памяти, так и благодаря возможности использования диодов с большим запасом по предельным режимам и повышению стабильности токов. 15

В- предложенном устройстве используется всего П. выравнивающих резисторов, где  — число групп;

Это позволяет сократить объем оборудования по сравнению с известным устрой- 20

4 ством, где на каждый диод устанавливается отдельный выравнивающий резистог.

Предмет изобретения

Йиодный дешифратор адресной выборки, содержащий диодные сборки, разделенные на группы, формирователи, накопитель, выравнивающие резисторы, о т л ич а ю шийся тем, что, с целью упро-, щения устройства и повышения его надежности, первые электроды всех диодных

l сборок каждой группы объединены и под\ I ключены через выравнивающий резистор к соответствующему формирователю, втос рые электроды L - : .х диодов K —, х диодных сборок всех групп объединены и соединены с (g ° К)-й шиной выборки накопителя.