Устройство для селекции асинхронных информационных потоков

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 478445

ИЗОБРЕТЕНИЯ

Союэ Советских

Социалкстимеских

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 18.12.72 (21) 1858686/26-9 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 25 07 76 Бюллетень 7 (45) Дата опубликования описания 22 О1 7 (51) М. Кл.

И 04) 3/06

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК

621 394,662(088 8) (72) А втор ы изобретения В. Б. Краскин и Л. В, Максимов (71) Заявитель (54) ус и ойство для селекции АсиихРоииых

ИНФОРМЛЦИОИЕ1ЫХ I ЮТОКОВ

Изобретение относится к связи и может

Г быть использовано в устройствах передачи данных.

Известно устройство для селекции асинхронных информационных потоков, содержашее fL индивидуальных блоков выборки каналоВ, В состав каждого из KQT0pb1x Входят запоминающий узел с узлом ввода на входе и узел опроса, причем ко входам узлов опроса подключены выходы блока фазирования и адаптивной коммутации, а выходы узлов опроса соединены с входами схем сборки адресных и информационных кодов.

Цель изобретения — йовысить надежность устройства. 1б

Для етого ня выходе схемы сборки адресных кодов подключен блок хранения и переадресации каналов, одна группа выходов которого через программный блок выборки каналов подключена к входам уз- 20 лов ввода индивидуальных блоков выборки каналов, я другая группа выходов через шифратор — к одному из входов буферного

1 запоминяюшего блока, к двум другим входам которого подключены соответственно l 25 выходы схемы сборки информационных ко- ! дов и блока фазирования и адаптивной ком мутации.

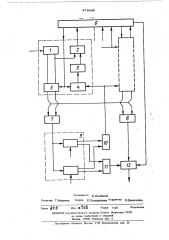

Иа чертеже изображена блок-схема пред ложенного устройства.

Устройство содержит tl. индивидуальных блоков выборки каналов, в состав каждого из которых входят входное устройство 1, схема сравнения 2, запоминаюший узел 3 с узлом ввода 4 на входе и узел опроса

5, входы которого соединены с выходами блока фазирования и адаптивной коммутации 6, а выходы соединены с входами схем 7 и 8 сборки адресных и информационных кодов, причем на выходе схемы

7 сборки адресных кодов подключен блок

9 хранения и переадресации каналов, одна группа выходов которого через программный блок 10 выборки каналов подсоединена к входам узлов ввода 4 индивидуальных блоков выборки каналов, 8 другая груп па Выходов через шифратор 11 — к одному из входов буферного зяпоминаюшего блока 1 2, к двум другим Входами которого подключены соответственно выходы схемы.1

478445

3 8 сборки информационных кодов и блока фазирования и адаптивной коммутации 6.

Устройство работает следуюшим образом.

На входы. и, индивидуальных блоков выборки каналов поступают асинхронные сигналы в виде кодов адреса каналов и ко.дов информации, передаваемой по этим канал

При совпадении кодов адреса канала, поступаюшего на вход входного устройства

1, и кода адреса, хранящегося в запоминающем узле 3, на выходе схемы. сравнения 2 выделится,сигнал равенства кодов.

Этот сигнал поступает в блок фазирования

l и адаптивной коммутации 6 и вызывает выделение сигнала считывания. Этот сигнал, воздействуя на узел опроса 5, производит считывание информации из входного устройства 1. При этом код адреса канала поступает через схему 7 сборки адресных кодов на. входы блока хранения 9 и переадресации каналов, где происходит сравнение кода адреса канала, который поступил в блок хранения 9, и кодов всех каналов, хранящихся в этом блоке. Совпадение кодов вызовет появление сигнала совпадения на выходах блока хранения 9.

Этот сигнал в шифраторе 1 1 преобразуется в код нового адреса канала, который соответствует адресу ячейки,выделившей сигнал. Сигналы нового коде адреса канала, воздействуя на входы буферного запоминающего блока 12, подготовят его к приему сигналов информации, передаваемой:, по выделенному каналу. Эти сигналы поступят на другие входы запоминающего блока

12 через схему 8 сборки информационных кодов.

В запоминаюшем блоке 12 информация хранится до очередного импульса считы4 . вания, который поступит от блока фазиро-! вания и адаптивной коммутации 6. Сигналы совпадения с выходов блока хранения

9 одновременно поступают и на входы

5 программного блока 10 выборки канала, из которого производится считывание адреса очередного выбираемого канала. Код а„, адреса очередного канала засылается в запоминающий узел 3 и хранится. там до

10 очередного совпадения в схеме сравнения

2. В дальнейшем цикл работы устройства повторяется по мере поступления сигналов на его входы.

15 Предмет изобретения1

Устройство для селекции асинхронных информационных потоков, содержащее tg индивидуальных блоков выборки каналов, в состав каждого из которых входят запоминающий узел с узлом ввода на входе и узел опроса, причем ко входам узлов опроса подключены выходы. блока фазирования и адаптивной коммутации, а вы25 ходы узлов опроса соединены с входами схем сборки адресных и информационных кодов, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, на выходе схемы сборки адресных кодов подключен

30 блок хранения и переадресации каналов, од4 на группа выходов которого через программный блок выборки каналов подключена к входам узлов ввода индивидуальных блоков

35 выборки каналов, а другая группа выходов через шифратор — к одному из входов буферного запоминающего блока, к двум другим входам которого подключены соответст- венно выходы схемы сборки информацион40 ных кодов и блока фазирования и адаптивной коммутации.

Составитель Е П гиблов

ОГИ ЛОВ

Редактор Т.Фадеева Техред Е. Пойурушина Корректор Л д

Заказ Изд. М К

Тираж 74Q Подписное

ЦНИИ11И 1 осударственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «11атент», Москва, Г-59, Бережковская наб., 24