Устройство синхронизации

Иллюстрации

Показать всеРеферат

Оп ИС Е (ii>473451

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических а"еспублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 03.О1.73 (21) 18696 18/26-9 (И) М, Кл.

H 04 (7/02 с присоединением заявки №Гасударственный намнтет йватв Мннватрав СССР па делам нэабретений и аткрытнй (23) Приоритет(43) Опубликцвано25.О7.75.Бюллетень №27 (53) УДК 621 316 ,727 (088.8) (45) Дата опубликования онисаиия21-о4 76

Ф. Г. Гордон, Л. Х Нурмухамедов и М. Я, Вертлиб (72) Авторы изобретения (7)) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

Изобретение относится к радиотехнике

;и может быть использовано в аппаратуре передачи данных и1ти аппаратуре контроля достоверности каналов.

Известные устройства синхронизации, содержащие последовательно соединенные формирователь импульсов и схему И" к э второму входу которой подключен выход задающего генератора через последовательно соединенные схему HET" и делитель, не обеспечивают требуемой частоты колебаний задающего генератора.

Целью изобретения является снижение частоты колебаний задающего генератора.

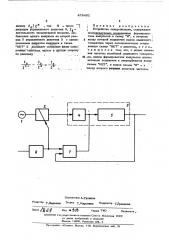

Для этого выход формирователя импульсов дополнительно подключен к запрещающему входу схемы НЕТ, а выход схемы "И - к входу второго разряда делителя частоты.

На чертеже изображена блок-схема предлагаемого устройства.

Устройство синхронизации состоит из ,задающего генератора 1, схемы "НЕТ" 2, управляемого делителя частоты 3, содерГ

1 i жащего первый разряд 4 и второй разряд

5 формирователя импульсов 6 и схемы

"И" 7.

Устройство работает следуюшим образом.

При отсутствии входной информации сигналы задающего генератора 1 делятся . управляемым делителем частоты 3 до ча» стоты, соотвеаствуюшей скорости переда.10 чи информации. При поступлении входной информации каждым ее фронтом с выхода . формирователя импульсов 6 осуществляется запрещение одного импульса задающего

15 генератора схемой НЕТ" 2 включенной

1 на входе первого разряда 4 управляемого делителя 3. Если тактовые импульсы на выходе управляемого делителя 3 находятся в зоне добавления, то фронтами информации в схеме "И" 7 формируется сиг« нал "Добавление, который поступает на вход второго разряда 5 управляемого дьлителя частоты 3. Запрет одного импульса в схеме "НЕТ" 2 вызывает смешение фазы синхронных тактовых частот на ве

478451

Составитель Д. 1 уцяКОВ

Редактор,фадеева Техред р Л иронева Корректор ТДфевцова заказ Д gg

Иад. Лй Щ

Тираж 740

Подписное °

Ц11ИИПИ Государственного комитета Совета Министров СССР по делам иэобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24 личину / П, где и - число l разрядов управляемого делителя 3 t p длительность элементарной посылки. Добавление одного импульса во второй разряд 5 управляемого делителя 3 с одновременным запретом импульса в схеме

НЕТ 2 рызывает смещение фазы синхронных тактовых частот в другую стоРону на величину

Предмет изобретени

Устройство синхронизации, содержащее последовательно соединенные формирователь импульсов и схему И, к второму входу которой подключен выход задающего генератора через последовательно соединенные схему НЕТ» и делитель, о т л и ч а ю щ е е с я тем, что, с целью снижения частоты колебаний задающего генератоЯ,ра, выход формирователя импульсов допол,, нительно подключен к запрещающему входу схемы НЕТ, а выход схемы И - к входу второго разряда делителя частоты. !