Способ цифрового измерения девиации сопротивления

Иллюстрации

Показать всеРеферат

О П И--O À -Н - И Е

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

< ц 479054

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 05.03.73 (21) 1887962/18-10 с присоединением заявки №вЂ” (23) Прио,ритет—

Опубликовано 30.07.75. Бюллетень № 28

Дата опубликования описания 01.03.76 (51) М. Кл. G Olr 27/00

Гасударственный комитет

Совета Министров СССР по делам изооретений и открытий (53) УДК 621.317.33 (088.8) (72) Авторы изобретения (71) Заявитель

В. С. Гутников и Х. Б. Аль-Рише

Ленинградский ордена Ленина политехнический институт им.М. И. Калинина (54) СПОСОБ ЦИФРОВОГО ИЗМЕРЕНИЯ ДЕВИАЦИИ

СОПРОТИВЛЕНИЯ

Способ цифрового измерения девиации сопротивления может быть применен для построения цифровых процентных омиетров, которые используются для определения разброса от номинала резисторов, выпускаемых промышленностью, а также для,построения цифровых измерителей девиации сопротивления или преобразуемых в нее неэлектрических величин.

Известные цифровые измерители девиации сопротивления построены по методу двухтактного интегрирования и позволяют получить результат измерения с высокой точностью. Для этого необходимо производить преобразование в два этапа: сначала девиацию сопротивления в напряжение, а затем— напряжение в цифровой код известным методом двухтактного или трехта ктного интегрирования. Это усложняет устройство измерения и увеличивает погрешность преобразования.

Цель изобретения — повышение точности измерений и обеспечение возможности выбора удобного масштаба преобразования с учетом определения знака девиации сопротивления.

Это достигается тем, что по предлагаемому способу длительность второго такта выбирают равной длительности первого такта и дополнительно вводят третий такт интегрирования, в течение которого на вход интегратора подают падение напряжения от упомянутого тока на резисторе с образцовым сопротивлением, уменьшенным в масштаб5 ный коэффициент раз, причем длительность третьего такта ограничивают временем, в течение которого выходное напряжение интегратора уменьшается до нуля, а в качестве результата измерения используют кодированное отношение длительности третьего такта к длительности одного из двух первых тактов.

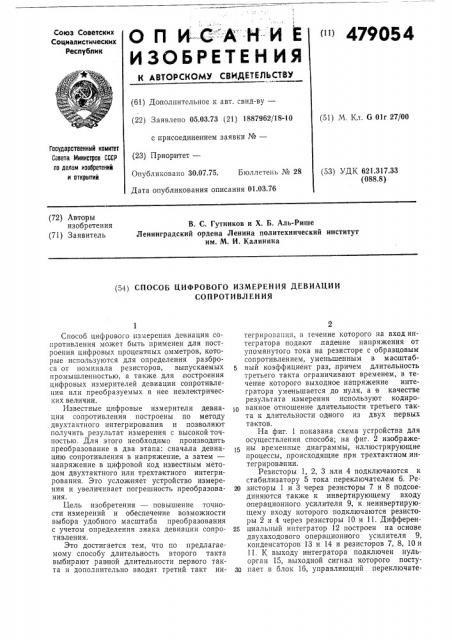

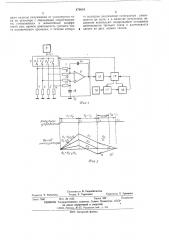

На фиг. 1 показана схема устройства для осуществления способа; на фиг. 2 изображены временные диаграммы, иллюстрирующие процессы, происходящие при трехтактном интегрировании.

Резисторы 1, 2, 3 или 4 подключаются к стабилизатору 5 тока переключателем 6. Ре20 зисторы 1 и 3 через резисторы 7 и 8 подсоединяются также к инвертирующему входу операционного усилителя 9, к неинвертирующему входу которого подключаются резисторы 2 и 4 через резисторы 10 и 11. Дифферен25 циальный интегратор 12 построен на основе двухвходового операционного усилителя 9, конденсаторов 13 и 14 и резисторов 7, 8, 10 и

11. К выходу интегратора подключен нульорган 15, выходной сигнал которого посту3о пает в блок 16, управляющий переключате479054

15 1 Π— Тст 1 0»

3 лем 6, ключом 17 и счетчиком 18. Через ключ 17 поступают импульсы опорной частоты fp, вырабатываемые в генераторе 19 импульсов, в счет»:к 18, выход которого сгяза» с блоком 16 управлен»я.

Измерительный цикл состоит из трех тактов и задается управляющими импульсами, которые вырабатываются в блоке управления прибора. В момент tp сбрасываются показания счетчика и на гинается его заполнение импульсами опорной частоты fp. В этот же момент tp начинается первый такт

Тг = Т, интегрирования, в течение которого резистор 1 подключается к стабилизатору тока переключателем 6 (положение а). На сопротивлении R образуется падение напряжения

U., I „Л,. = 1 „(РОЛЛ,.), где 1„— ток стабилизатора 5;

R Ä— = Rp» ËR — сопротивление резистора 1;

+hR, — измеряемая девиация сопротивления R „, и происходит интегрирование напряжения U„, подведенного к инвертирующему входу операционного усилителя. В момент — (конец первого такта интегрирования) преобразуется напряжение на выходе интегратора. т

° I,. (Rp AR „), где т=ЯС вЂ” постоянная времени цепи обратной связи интегратора;

ТΠ— первый такт интегрирования, который определяется первым переполнением счетчика.

Счетчик устанавливается в исходное нулевое состояние в процессе его переполнения импульсами опорной частоты fp. При этом с блока управления поступает команда, выделяющая окончание первого такта интегрирования. В этот же момент 4 начинается второй такт интегрирования T» = ТО, в течение которого резистор 2 подключается к стабилизатору тока (положение б переключателя 6). На этом резисторе образуется падение напряжения где Rp —:сопротивление образцового резистора 2.

Это напряжение интегрируется в противоположном направлении, так как оно подается на неинвертирующий вход интегрирующего усилителя. В момент второго переполнения счетчика поступает соответствующая команда с блока управления и кончается второй такт интегрирования.

B этот же момент t2»ачинается третий такт интегрирования Т ш = 1„в течение которого резисторы 3 или 4 подключаются к стабилизатору тока (положение в или г пе20

55 б0

4 рек.;»очателя 6). Это зависит от знака девиации сопротивления, который о»ределяется олоком управления приоора: минус в случае, если выходное напряжение интегратора переходит через нуль до второго переполнения счетчика, т. е. до момента t, и плюс, если выходное напряжение интегратора достигает нуля после момента tq. B случае отрицательного знака девиации сопротивления из блока управления команда, фиксирующая конец измерения, не поступает до момента t .

На резисторах 3 или 4 образуется паде»ие напряжения где

R0 — сопротивление любого из

m резисторов 3 или 4. Это напряжение интегрируется в том же или в противоположном направлении интегрирования U p в зависимости от знака девиации сопротивления. Кроме того, .интегрирование в этом такте происходит с наклоном, в m раз меньшим, чем в предыдущих тактах, что увеличивает чувствительность преобразования в т раз. Как только выходное на пряжение интегратора достигает нуля, вырабатывается стоп-импульс, определяющий конец третьего такта (момент t3) и закрывается ключ 17.

Относительная измеряемая девиация сопротивления линейно связана с относительным показанием счетчика, которое не зависит от постоянной времени т RC-цепи интегратора и не зависит от тока стабилизатора I„„.

При известном отношении преобразования неэлектрических величин в сопротивление, выбирая m, можно получить показание счетчика, выражающее результат измерения непосредственно в единицах измеряемой величины. При этом чувствительность измерения определяется емкостью счетчика. Входящий в схему стабилизатор тока реализуется по простой схеме, так как его нестабильность не вносит погрешности в результат измерения.

Предмет изобретения

Способ цифрового измерения девиации сопротивления, основанный на интегрировании в течение первого такта падения напряжения от некоторого тока на резисторе, девиацию сопротивления которого необходимо измерить, и в течение второго такта — паде»ия напряжения от того же тока на резисторе с образцовым сопротивлением, атличаюи1ийся тем, что, с целью повышения точности измерений и обеспечения возможности выбора удобного масштаба преобразования с учетом определения знака девиации сопротивле»ия, длительность второго такта выбирают равной длительности первого такта и дополнительно вводят третий такт интегрирования, в течение которого на вход интегратора по479054

Импульсы рпра 5пенир

Выл од

ИнтЕгратОР

Составитель В. Скоробогатова

Техред 3. Тараненко Корректор Т. Гревцова

Редактор T. Рыбалова

Заказ 7688 Изд. № 1653 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

МОТ, Загорский филиал дают падение напряжения от упомянутого тока а резисторе с образцовым сопротивлением, уменьшенным в масштабный коэффициент раз, причем длительность третьего такта ограничивают временем, в течение которого выходное напряжение интегратора уменьшается до нуля, а в качестве результата измерения используют кодированное отношение длительности третьего такта к длительности

S одного из двух первых тактов.