Цифровой регулятор

Иллюстрации

Показать всеРеферат

1 .

g-мбл и О-1

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (6I) Дополнительное к авт. свид-ву— (22) Заявлено 02,01.73 (21) 1871381/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 30.07.75. Бюллетень № 28

Дата опубликования описания 12.03.76 (51) М. Кл. G 05b 11/26

Государственный комитет

Совета Министров СССР во делам нэооретеннй н открытий (53) УДК 62-504.3(088.8) (72) Автор изобретения

Д. Хачатуров (71) Заявитель

Ордена Трудового Красного Знамени институт физики

АН Грузинской ССР (54) ЦИФРОВОЙ РЕГУЛЯТОР

Изобретение относится к области технической кибернетики. и может быть использовано в системах автоматизации постановки научного эксперимента и технологических процессов.

Известен цифровой регулятор, выполняющий функцию стабилизации параметра на заданном уровне, содержащий блок сравнения, соединенный через сумматор с цифро-аналоговым преобразователем, а также с задатчиком кода, блоком управления и аналого-цифровым преобразователем, соединенным с блоком управления.

В предложенном устройстве расширение функциональных возможностей регулятора достигается тем, что в пем установлены связанный со входом блока управления пороговый блок, подключенный к пороговому блоку и блоку сравнения сумматор-задатчик и соединенный с сумматором-задатчиком и сумматором блок совпадения, подключенный входами к задатчику кода, блоку управления и блоку сравнения.

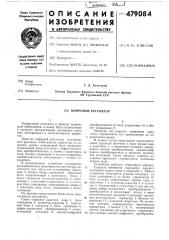

На чертеже представлена блок-схема предлагаемого регулятора.

Схема содержит задатчик кода 1, блок совпадения 2, сумматор-задатчик 3, пороговый блок 4, сумматор 5, блок сравнения 6, цифро-аналоговый преобразователь 7, исполнительный механизм 8, аналого-цифровой

2 преобразователь 9, блок управления 10 и объект управления 11.

Известно, что скорость изменения параметра определяется его приращением за определенное время.

В нашем случае приращение представляет собой заданную величину в виде порции кода в задатчике 1, а временной интервал определяется циклом преобразования аналого-циф>р рового преобразователя и является постоянной величиной. Таким образом, скорость изменения параметра определяется величиной порции кода.

Устройство работает следующим образом.

Скорость изменения параметра задается величиной порции кода в задатчике 1. Работ» устройства начинается подачей импульса на блок совпадения 2 из блока управления 10.

Этот импульс переписывает порцию кода из

2ð задатчика 1 в сумматор-задатчик 3 и сумматор 5. Записанный в сумматоре 5 код прп помощи цифро-аналогового преобразователя 7 преобразуется в аналоговый сигнал и через исполнительный механизм 8 вызывает измене25 ние регулируемого параметра в объекте управления 11 с заданной скоростью. По истечении времени, определяемого переходными процессами в блоках 7, 8, 11, непрерывный сигнал (величина регулируемого параметра)

Зр при помощи аналого-цифрового преобразова479084

Составитель Ю. Шувалов

Техред А. Камышникова Корректор Т. Гревцова

Редактор Н. Коляда

Заказ 7689 Изд. 1655 Тираж 869 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д, 4/5

МОТ, Загорский филиал

3 теля 9 преобразуется в цифровой код и в блоке сравнения 6 сравнивается с кодом, записанным в сумматоре-задатчике 3. Если код с выхода аналого-цифрового преобразователя

9 не равен заданному (что говорит об отклонении скорости изменения регулируемого параметра от заданной), то сравнивающий блок определяет разность кодов, которая в зависимости от знака суммируется с содержимым или вычитается из содержимого сумматора 5.

Далее эта разность через цифро-аналоговый преобразователь 7 и исполнительный механизм 8 корректирует скорость изменения параметра в объекте управления 11. При равенстве кодов на обоих входах блока сравнения

6, последний вырабатывает импульс, который через блок совпадения 2 переписывает следующую порцию кода из задатчика 1 в сумматор-задатчик 3 и сумматор 5. В результате этого в этих сумматорах оказывается код, равный сумме двух порций, Далее цикл повторяется.

После набора задан ной суммы кодов в сумматоре-задатчике 3 срабатывает пороговый блок 4, который через блок управления

10 снимает разрешение перезаписи кода из задатчика 1 в другие блоки. После этого регулятор работает как стабилизатор параметра на заданном уровне, определяемом суммарным кодом.

Режим уменьшения параметра с постоянной скоростью обеспечивается вычитанием порции кодов из содержимых сумматора-задатчика 3 и сумматора 5.

Таким образом, при помощи предлагаемой схемы цифрового регулятора можно выполнять следующие функции: поддерживать постоянство скорости (линейность) изменения параметра, регулировать скорость изменения

1о параметра, поддерживать параметр на заданном уровне.

Предмет изобретения

Цифровой регулятор, содержащий задатчик кода и блок управления, соединенный с блоком сравнения и аналого-цифровым преобразователем, подключенным через блок

20 сравнения и сумматор к цифро-аналоговому преобразователю, отличающийся тем, что, с целью расширения функциональных возможностей, в нем установлены связанный со входом блока управления пороговый блок, под25 ключенный к пороговому блоку и блоку сравнения сумматор-задатчик и соединенный с сумматором-задатчиком и сумматором блок совпадения подключенный входами к задатчику кода, блоку управления и блоку сравне30 ния.