Устройство для централизованного контроля

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ "1 479И9

Союз Советский

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.07.73 (21) 1950020/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 30.07,75. Бюллетень № 28

Дата опубликования описания 15.09.76 (51) М. Кл, G 06f 15/46

Государственный комитет

Саввта Министров СССР па делам изобретений и аткрытий (53) УДК 681.17(088.8) (72) Авторы изобретения

В. Ф. Бахмутский, А. Б. Кметь, И. Б. Мелихов, О. Л. Николайчук, М. А. Раков, В, С. Якушев и Э. П. Дзисяк

Львовский завод электроизмерительных приборов и Физико-механический институт АН Украинской ССР (71) Заявители (54) УСТРОЙСТВО ДЛЯ ЦЕНТРАЛИЗОВАННОГО КОНТРОЛЯ

Изобретение относится к системам централизованного контроля с временным разделением каналов и цифровой регистрацией.

Известно устройство для централизованного контроля с временным разделением каналов и цифровой регистрацией, содержащее датчики, соединенные с блоками измерения, коммутатор, аналого-цифровой преобразователь, цифровой регистратор, генератор тактовых импульсов, счетчик, дешифратор-распределитель, задатчик фазовых уставок, компараторы, блок допускового контроля и блок управления. Однако для обеспечения высокой точности измерения и контроля необходимо предъявлять к узлам прямого тракта преобразования жесткие метрологические требования, реализация которых связана со значительными затратами.

Цель изобретения — повышения точности измерения и контроля. Это достигается тем, что в предлагаемое устройство дополнительно введены управляемый ключ, дифференциальные усилители, управляемые элементы памяти, генератор ступенчатого напряжения, аналоговые сумматоры, генератор опорных импульсов, масштабные преобразователи фазы в напряжение и напряжения в фазу, причем выходы задатчика фазовых уставок совместно с выходами масштабных преобразователей на2 пряжения в фазу соединены с входами компараторов. выходы которых подключены к блоку допускового контроля, выходом соединенного с одним из входов цифрового регистратора, а входом — с входом аналого-цифрового преобразователя и выходом блока управления, два других входа цифрового регистратора соединены с блоком управления и аналого-цифровым преобразователем, вход которого под1р ключен к выходу коммутатора, входы последнего подключены к выходам дешифраторараспределителя и масштабных преобразователей напряжения в фазу, вход блока управления соединен с генератором тактовых им15 пульсов, а выход — с управляемым ключом, выходы блоков измерения соединены с дифференциальными усилителями и аналоговыми сумматорами, выходы которых подключены к входам масштабных преобразователей напря20 жения в фазу, а входы — к выходам управляемых элементов памяти, входы которых соединены с дифференциальными усилителями и коммутатором, выход генератора опорных импульсов соединен через генератор ступенчато25 ro напряжения с генератором тактовых импульсов, выход последнего через управляемый ключ и счетчик подключен к дешифраторураспределителю, масштабный преобразователь фазы в напряжение, соединенный с генерато30 ром ступенчатого напряжения, подключен к

3 коммутатору и дифференциальным усилизелям.

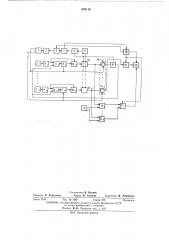

На чертеже представлена схема предлагаемого устройства.

Устройство содержит дешифр а гор-р аспределитель 1, датчики 21 — 2„, счетчик 3, блоки измерения 4> — 4,, управляемый ключ 5, дифференциальные усилители 61 — 6„, генератор

7 тактовых импульсов, управляемые элементы 8> — 8„, генератор 9 ступенчатого напряжения, аналоговые сумматоры 101 — 10Ä, генератор 11 опорных импульсов, грубые масштабные преобразователи 12> — 12„напряжения в фазу (Н вЂ” Ф), задатчики 13 фазовых уставок, коммутатор 14, компараторы фаз

151 — 15,, точный масштабный преобразователь 16 фазы в напряжение (Ф вЂ” Н), блок 17 допускового контроля, блок 18 управления, аналого-цифровой преобразователь (АЦП) 19, цифровой регистратор 20.

Устройство для централизованного контроля работает следующим образом.

Контролируемые параметры с датчиков

21 — 2„поступают на блоки измерения 41 — 4 „ и снимаются с них в виде изменяющихся напряжений U»,. (U„,..., U,), которые поступают постоянно на входы аналоговых сумматоров 10 и дифференциальных усилителей 6.

Один раз за цикл обегания всех каналов (последовательно для каждого канала) поступающее на вход дифференциального усилителя 6; напряжение разбаланса ЛУ; = U»;— — U„U — напряжение на выходе масштабного преобразователя Ф вЂ” Н 16), фиксируемое управляемым элементом памяти 8,. (сигнал включения памяти подается синхронно с сигналом включения соответствующей позиции коммутатора) и суммируемое с U; в аналоговом сумматоре 10,, отрабатывается по цепи обратной связи до нуля, т. е. до равенства U„,. =U,,, При этом на входы остальных сумматоров поступают напряжения

U„j и ЛУ/, где ЛУ. — напряжение на выходе управляемого элемента памяти 8,, полученное в предыдущем цикле обегания (элементы памяти управления отключены от входов дифференциальных усилителей и сохраняют свое состояние).

Ниже приводятся расчетные соотношения.

V=k (У « - U). (1) где ср — фаза; йц — коэффициент преобразования одного преобразователя Н вЂ” Ф.

U„ =kу kg (У +ЛУ), (2) где k — коэффициент преобразования одного преобразователя Ф вЂ” Н.

ЛУ ° Й, = (У « — У ) Й =.ЛУ, (3) где Й вЂ” коэффициент усиления одного дифференциального усилителя 6.

Из (1), (2), (3) при 1 )) 1 получают

479119

U„(1 — Ау /г - )=ЛУЯн kÄ.+1/kу) :=ЛУ йц /с

U,. (1 — km /г ) = ((p — k.. U,.)ku, откуда

U Ä â€” — ku ° <р. (4)

Выражение (4) показывает, что точность преобразования определяется точным обратным преобразователем Ф вЂ” Н, а звенья прямого тракта преобразования Н вЂ” Ф могут быть достаточно грубыми.

Предлагаемое устройство работает следующим образом.

Пусть коммутатор 14 находится на первой отрабатываемой позиции контроля, т. е. дешифратор-распределитель 1, управляемый счетчиком 3, на который подаются импульсы с генератора 7 через управляемый ключ 5, выдает разрешение на подключение управляемого элемента памяти 8> к дифференциальному усилителю 6ь Предположим, что элемент памяти предварительно разряжен, т. е. сигнал на его выходе равен нулю. Контролируемый параметр — напряжение U, — с выхода аналогового сумматора 10 поступает íà грубый преобразователь Н вЂ” Ф 12ь который преобразует его с некоторой погрешностью в фазу импульсной последовательности. С выхода

30 преобразователя 12> фаза подается на вход точного преобразователя 16 Ф вЂ” Н, выход которого соединен с одним из входов дифференциального усилителя 6ь С выхода дифференциального усилителя 6, напряжение разбаланса, равное AU>=k (U — U„, ) =,, ° ЛУь поступает на вход управляемого элемента памяти 8ь с выхода которого оно подается на аналоговый сумматор 10 . Напряжение разбаланса ЛУ суммируется в аналоговом сумма40 торе 101 с напряжением контролируемого параметра U„,, и на вход преобразователя

Н вЂ” Ф 12, поступает напряжение, равное

У„, +ЛУ,.

По цепи обратной связи (Н вЂ” Ф) — (Ф вЂ” Н)

45 происходит отслеживание до момента выравнивания напряжений прямого и обратного тракта U и U, т. е. до ЛУ вЂ” — О.

На время отслеживания (коррекция прямого тракта преобразования) запрещается.про50 хождение тактовых импульсов с генератора 7 через ключ 5 на счетчик 3. Запрет осуществляется блоком 18 управления. Блок управления выдает также сигнал запрета во время коррекции на АЦП 19 и цифровой регистратор

55 20 и при необходимости на блок 17 допускового контроля. Каждый канал корректируется один раз за цикл опроса (т. е. за и циклов опроса корректируются все и каналов), при этом остальные (некорректируемые) каналы опра60 шиваются с частотой генератора 7. Контролируемые сигналы с выхода коммутатора 14 подаются на АЦП 19 и далее регистрируются регистратором 20. Частота генератора 7 тактовых импульсов синхронизирована с часто55 той генератора 9 ступенчатого напряжения и, 479119

5 в свою очередь, синхронизирует работу блока

18 управления, Частота f„, генератора 9 связана с частотой f> генератора 11 опорных импульсов зависимостью где ш — число состояний многозначного элемента, образованного грубым преобразователем Н вЂ” Ф 12 и точным преобразователем

Ф вЂ” Н 16.

Компараторы фаз 15> — 15„сравнивают фазы контролируемых параметров с выходов преобразователей Н вЂ” Ф 12 — 12 „с предустанавливаемыми фазами задатчика 13. Сравнение происходит в динамике, признаки сравнения поступают на блок 17 допускового контроля, который вырабатывает сигналы «Больше», «Меньше», «Норма» и управляет работой регистратора 20, устраняя избыточность регистрируемых данных.

К числу преимуществ предлагаемого устройства относится наличие одного точного преобразователя Ф вЂ” Н и и грубых преобразователей Н вЂ” Ф, что позволяет значительно сократить расход оборудования в системе при заданной точности или повысить точность при заданных аппаратурных затратах. Не предьявляются жесткие требования и к элементам памяти, которые запоминают не полный уровень сигнала U„,, а только сигнал коррекции, т. е. рассогласование уровней U»; и U вызва нное дрейфом характеристик прямого тракта преобразования, Дифференциальные усилители 6 должны иметь только высокую чувствительность, высокая стабильность параметров от них не требуется, как и для других звеньев прямого тракта преобразования (сумматоров, преобразователей Н вЂ” Ф).

Применение многозначных элементов (H — Ф) — (Ф вЂ” Н) с фазовым управлением дает существенную экономию в количестве тактирующих и раавертывающих устройств, которые являются общими для всей системы и осуществляют жесткую синхронизацию всех каналов, что облегчает считывание и сопряжение с внешними устройствами.

Зо

6

Предмет изобретения

Устройство для централизованного контроля, содержащее датчики, соединенные с блоками измерения, коммутатор, аналого-цифровой преобразователь, цифровой регистратор, генератор тактовых импульсов, счетчик, дешифратор-распределитель, задатчик фазовых уст а во к, коми ар а торы, блок допускового контроля и блок управления, отличающееся тем, что, с целью повышения точности измерения и контроля, в устройство дополнительно введены управляемый ключ, дифференциальные усилители, управляемые элементы памяти, генератор ступенчатого напряжения, аналоговые сумматоры, генератор опорных импульсов, масштабные преобразователи фазы в напряжение и напряжения в фазу, причем выходы задатчика фазовых уставок совместно с выходами масштабных преобразователей напряжения в фазу соединены с входами компараторов, выходы которых подключены к блоку допускового контроля, выходом соединенного с одним из входов цифрового регистратора, а входом — с входом аналого-цифрового преобразователя и выходом блока управления, два других входа цифрового регистратора соединены с блоком управления и аналого-цифровым преобразователем, вход которого подключен к выходу коммутатора, входы последнего подключены к выходам дешифратора-распределителя и масштабных преобразователей напряжения в фазу, вход блока управления соединен с генератором тактовых импульсов, а выход — с управляемым ключом, выходы блоков измерения соединены с дифференциальными усилителями и аналоговыми сумматорами, выходы которых подключены к входам масштабных преобразователей напряжения в фазу, а входы — к выходам управляемых элементов памяти, входы которых соединены с дифференциальными усилителями и коммутатором, выход генератора опорных импульсов соединен через генератор ступенчатого напряжения с генератором тактовых импульсов, выход последнего через управляемый ключ и счетчик подключен к дешифратору-распределителю, масштабный преобразователь фазы в напряжение, соединенный с генератором ступенчатого напряжения, подключен к коммутатору и дифференциальным усилителям.

479119

Составитель В. Яушей

Техред М. Семенов

Корректор M. Лейзерман

Редактор Е. Караулова

Заказ 3103

МОТ, Загорский филиал

Изд. Мз 1680 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5