Устройство для асинхронного уплотнения каналов связи с использованием временного разделения сигналов

Иллюстрации

Показать всеРеферат

ОПИСАН И

ИЗОБРЕТЕН И

К АВТОРСКОМУ СВИДЕТЕДЬС

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 16.02.73 (21) 1884317/18с присоединением заявки ¹

15/06

3/00

32) Пр тор риоритет

Совета Министров СССР по делаи изобретений и открытий

Опубликовано 30.07.75. Бюллетень № 2

Дата опубликования описания 09,10.75

88.8) (72) Авторы изобретения

И. В. Мягков, Г. П. Абугов и В. Ф. Зенкин

Центральный научно-исследовательский институт связи (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО УПЛОТНЕНИЯ

КАНАЛОВ СВЯЗИ С ИСПОЛЬЗОВАНИЕМ ВРЕМЕННОГО

РАЗДЕЛЕНИЯ СИГНАЛОВ

Изобретение относится к электросвязи и может использоваться в аппаратуре асинхронного ввода двоичной информации в синхронный тракт.

Известны устройства асинхронного ввода с импульсным стаффингом, содержащие на передающей станции блок эластичной памяти, фазовый компаратор, формирователь команд, блок изменения темпа считывания и передатчик групповой синхронизации, а на приемной станции — приемник групповой синхронизации, дешифратор команд, блок изменения темпа записи, блок эластичной памяти и генератор с фазовой автоподстройкой частоты (ФАПЧ) . В этих устройствах согласование фазы асинхронного входного сигнала на передаче и восстановленного сигнала на приеме с временными позициями канала связи осуществляется блоками эластичной памяти, каждый из которых состоит из распределителя записи, ячеек записи, ячеек памяти распределителя считывания, ячеек считывания и схемы «ИЛИ». При этом на тактовой частоте входного и выходного сигналов работают не только связанные с ней непосредственно внешние распределители (распределители записи на передаче и считывания на приеме), но и связанные с каналом связи внутренние распределители (распределители считывания на передаче и записи на приеме), у которых эта частота формируется из тактовых импульсов канала связи путем исключения или вставки импульсов на временных позициях стаффинга.

Обычно канал управления стаффингом образуют путем периодической вставки его посылок между посылками основного канала.

При этом, поскольку импульсы считывания на передаче и записи на приеме оказываются размещенными неравномерно, импульсы внутренних распределителей, управляющие работой фазового компаратора и схемы ФАПЧ, смещаются за счет стаффинга то на один, то на два тактовых интервала частоты канала связи. Так как работа внутренних распределителей не связана со сверхцикловой синхронизацией, величина шагов коррекции на передаче и на приеме может оказаться различной, что в ряде случаев приводит к увеличению низкочастотных фазовых флуктуаций выход20 ного сигнала.

Для того чтобы избавится от этих недостатков, в предлагаемое устройство введены на передающей станции блок изменения последовательности записи и блок выделения

25 временной позиции стаффинга, причем выход блока изменения последовательности записи через распределитель записи подключен к первому входу блока выделения временной позиции стаффпнга, к второму входу под30 ключен второй выход передатчика групповой

479138 синхронизации, выход блока выделения временной позиции стаффинга и выход формирователя команд подключены к входам управления блока изменения последовательности, m выходов импульсов считывания передатчика групповой синхронизации подключены к соответствующим входам т ячеек считывания, последний выход передатчика групповой синхронизации подключен к второму входу фазового компаратора, а на приемной станции — блок измерения последовательности считывания и блок выделения временной позиции стаффинга, причем т выходов импульсов записи приемника групповой синхронизации подключены к соответствующим входам каждой из т, ячеек записи, последний выход приемника групповой синхронизации соединен с вторым входом генератора с

ФАПЧ, выход генератора с ФАПЧ соединен с входом блока изменения последовательности считывания, входы управления которого соответственно подключены к выходам дешифратора команд и блока выделения временной позиции стаффинга, входы которого соединены с выходом распределителя считывания и выходом приемника групповой синхронизации.

В устройстве коррекция фазовых сдвигов производится путем воздействия на внешние распределители. При этом работа внутренних распределителей оказывается связанной с частотой сверхциклов, причем для нескольких устройств асинхронного ввода могут быть использованы общие внутренние распределители, Это позволяет включить внутренние распределители в состав устройств групповой синхронизации, а в случае кратности числа посылок в сверхцикле объему эластичной памяти непосредственно использовать в качестве внутренних распределителей делители групповых устройств синхронизации.

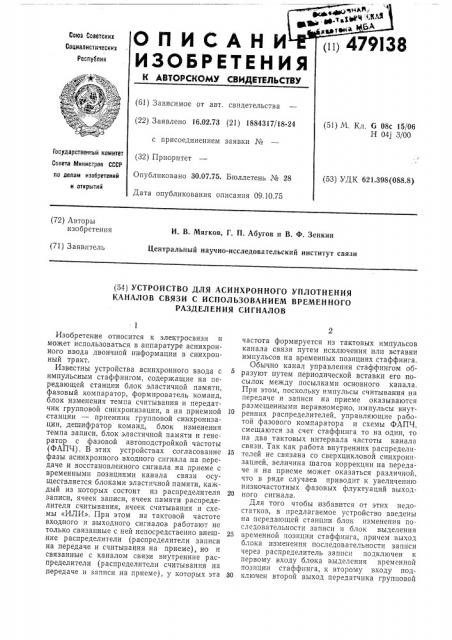

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит блок 1 изменения последовательности записи, блок 2 выделения временной позиции стаффинга, распределитель 3 записи, формирователь 4 команд, фазовый компаратор 5, передатчик б групповой синхронизации, ячейки 7 — 9 записи, ячейки

10 — 12 памяти, ячейки 13 — 15 считывания, схему «ИЛИ» 16, дешифратор 17 команд, приемник 18 групповой синхронизации, генератор 19 с ФАПЧ, блок 20 изменения последовательности считывания, распределитель 21 считывания, блок 22 выделения временной позиции стаффинга, ячейки 23 — 25 записи, ячейки 26 — 28 памяти, ячейки 29 — 31 считывания, схему «ИЛИ» 32.

Устройство работает следующим образом.

При положительном стаффинге на передающей станции информационный сигнал при помощи распределителя 3 записи записывается в ячейки 10, 11 и 12 памяти, а затем считывается на ячейках 13, 14, 15 m-импульсными

f. последовательностями с частотой — кажт дая, формируемыми передатчиком б групповой синхронизации. В простейшем случае, когда число информационных посылок в сверхцикле кратно m, сигнал из каждой ячейки памяти всегда попадает на определенные тактовые позиции сверхцикла. Когда фазовый сдвиг между импульсами записи и считывания достигает определенной величины, фиксируемой фазовым компаратором 5, срабатывает формирователь 4 команд, и по дополнительному каналу связи передается команда, соответствующая передаче балластной посылки.

В конце сверхцикла за т тактовых интервалов до временной позиции, на которой может передаваться балластная посылка, передатчик 6 групповой синхронизации включает блок 2 выделения временной позиции стаффинга. Поскольку импульсы записи и считывания одной ячейки памяти во времени никогда не совпадают, временной сдвиг между ними всегда больше нуля, но меньше m тактовых интервалов. Дает возможность блоку 2 выделить

25 из последовательности импульсов записи определенной и-й ячейки памяти импульс, вписывающий в эластичную память посылку, передаваемую непосредственно перед балластной посылкой. По окончании этого импульса, при

30 наличии сигнала от формирователя 4 команд о необходимости передачи балластной посылки, блок 1 изменения последовательности записи воздействует на распределитель 3 записи, который производит вписывание очеред35 ной информационной посылки не в (а+1)-ю, а в (n+2) -ю ячейку памяти, Таким образом, посылка, считываемая из (и+1)-й ячейки памяти, оказывается балластной.

На приемной станции линейный сигнал, 40 принятый по основному каналу при помощи m

Ун импульсных последовательностеи — от

m приемника 18 групповой синхронизации, последовательно вписывается ячейками 23, 24 и

45 25 записи в ячейки 26, 27 и 28 памяти.

Тактовая частота асинхронно передаваемого сигнала fc восстанавливается генератором с ФАПЧ 19. Распределитель 21 считывания формирует из этой частоты т импульсных по50 следовательностей —, которые на ячеиках

fc

v т

29, 30 и 31 считывают сигнал из ячеек памяти. Считанный сигнал через схему «ИЛИ» 32 поступает на выход устройства.

На тактовой позиции, на которой может передаваться балластная посылка, приемник 18 групповой синхронизации на m тактовых интервалов открывает блок 22 выделения временной позиции стаффинга. Блок 22 из после60 довательности считывающих импульсов и-й ячейки памяти выделяет импульс, считывающий информационную посылку, предшествующую балластной. По окончании этого импульса при приеме дешифратором 17 команды о

65 наличии в принятом цифровом потоке бал479138 ластной посылки блок 20 изменения последовательности считывания воздействует на распределитель 21 считывания, который очередное считывание производит не из (и+1)-й, а из (г+2)-й ячейки памяти. Таким образом, балластная посылка исключается из принятого сигнала.

При отрицательном или двустороннем стаффинге компенсация фазовых сдвигов осуществляется за счет передачи части информационных посылок по дополнительному каналу.

В этом случае, после выделения блоком 2 импульса, считывающего предшествующую информационную посылку, блок 1 останавливает распределитель 3 записи на один такт, запрещая вписывание в основные ячейки памяти, а блок 2 выдает импульс, записывающий очередную посылку в дополнительную ячейку памяти. Эта посылка передается из тактовой позиции дополнительного канала, записывается на приемной станции в дополнительную ячейку и при срабатывании блока 20, останавливающего распределитель 21 считывания, вписывается в восстанавливаемый сигнал импульсом блока 22.

В общем случае число информационных посылок в сверхцикле может быть не кратным

m. При этом для того, чтобы сигнал каждой ячейки памяти передавался на одних и тех же тактовых позициях суперцикла, можно при помощи блоков 1 и 2 в одном или нескольких определенных местах сверхцикла производить пропуск записи в одну из ячеек памяти на передаче и при помощи блоков 20 и 22 — соответствующий пропуск считывания на приеме.

Выбор таких мест сверхцикла с учетом неравномерности импульсной последовательности f позволяет сохранить объем эластичной памяти равным и бит. В то же время используемая в определенном месте сверхцикла ячейка памяти может быть использована вместо дополнительной ячейки памяти при отрицательном или двустороннем стаффинге.

Таким образом, устройство обеспечивает асинхронный ввод дискретной информации в синхронный такт и восстановление этой информации на приемной станции. Коррекция временных сигналов осуществляется путем воздействия на внешние распределители без изменения количества импульсов записи и считывания эластичной памяти. Это позволяет формировать последовательности импульсов считывания на передаче и импульсов записи на приеме в блоках групповой синхронизации. При этом устраняется возможность увеличения фазовых флуктуаций выходного сигнала при использовании неравномерной последовательности тактовых позиций основного канала связи. Одновременно за счет исключения внутренних распределителей из состава индивидуальной аппаратуры достигается значительное упрощение аппаратуры асинхронного ввода методом стаффинга.

l0

55 б0

Предмет изобретения

Устройство для асинхронного уплотнения каналов связи с использованием временного разделения сигналов, содержащее на передающей станции распределитель записи, соответствующие выходы которого подключены к первым входом т ячеек записи, пОследний выход распределителя записи соединен через фазовый компаратор с первым входом формирователя команд, вторые входы m ячеек памяти записи объединены, а выходы через соответствующие ячейки памяти подключены к входам каждой из т ячеек считывания, выходы которых через схему «ИЛИ» подключены к линии связи, первый выход передатчика групповой синхронизации подключен к второму входу формирователя команд, а на приемной станции одни входы m ячеек записи объединены, выходы m ячеек записи через соответствующие ячейки памяти подключены к одним входам соответствующих т ячеек считывания, другие входы которых соединены с соответствующими выходами распределителя считывания, а выходы подключены к схеме

«ИЛИ», последний выход распределителя считывания подключен к первому входу генератора с фазовой автоподстройкой частоты, дешифратор команд соединен с приемником групповой синхронизации, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности работы и упрощения устройства, в него введены на передающей станции блок изменения последовательности записи и блок выделения временной позиции стаффинга, причем выход блока изменения последовательности записи через распределитель записи подключен к первому входу блока выделения временной позиции стаффинга, к второму входу подключен второй выход передатчика групповой синхронизации, выход блока выделения временной позиции стаффинга и выход формирователя команд подключены к входам управления блока изменения последовательности записи, m выходов импульсов считывания передатчика групповой синхронизации подключены к соответствующим входам m ячеек считывания, последний выход передатчика групповой синхронизации подключен к второму входу фазового компаратора, а на приемной станции — блок изменения последовательности считывания и блок выделения временной позиции стаффинга, причем m выходов импульсов записи приемника групповой синхронизации подключены к соответствующим входам каждой из т ячеек записи, последний выход приемника групповой синхронизации соединен с вторым входом генератора с фазовой автоподстройкой частоты, выход генератора с фазовой автоподстройкой частоты соединен с входом блока изменения последовательности считывания, входы управления которого соответственно подключены к выходам дешифратора команд и блока выде479138 номады

Составитель H. Лысенко

Техред М. Семенов

Корректор Е. Рогайлина

Редактор Е. Караулова

Заказ 2486/16 Изд. № 1649 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР— по делам изобретений и открытий

Москва, 3К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ления временной позиции с ффифр, входы которого соединены с выходом фЪ3ц и елите

:Ъ ф,„ ь ля считывания и выходом приемника групповой синхронизации.