Интегральное запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е щ 479153

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВЙДЕТЕДЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.05.73 (21) 1919979/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.75. Бюллетень № 28

Дата опубликования описания 14.10.75 (51) М. Кл. G 1lс 11/40

Государствеиимй комитет

Совета Мииистров СССР по делам изобретеиий и открытий (53) P ÄÊ 681.327.67 (088.8) (72) Авторы изобретения

А. И. Мальцев, А. П. Нагин, В. В. Поспелов и Ю. P. Чернышев (71) Заявитель (54) ИНТЕГРАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники.

Известны интегральные запоминающие устройства, содержащие выполненную в изолированной области матрицу накопителя на

МДП-транзисторах с изменяемым пороговым напряжением и дешифратор строк на МДПтранзисторах.

Однако из-за необходимости коммутации дешифратором относительно высоковольтных сигналов усложняются разработка и изготовление схемы и снижается ее надежность. Кроме того, в таких устройствах используются

МДП-транзисторы, имеющие одинаковые по знаку пороговые напряжения на их характеристиках перезаписи.

Цель изобретения — улучшение эксплуатационных характеристик и технологичности запоминающего устройства.

Это достигается тем, что предлагаемое устройство содержит дополнительные управляющие транзисторы, затворы которых подключены к шине управляющего сигнала, стоки — к выходным шилам дешифратора столбцов, а истоки — к шинам столбцов матрицы накопителя.

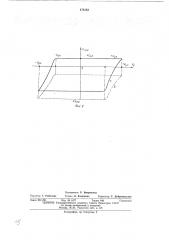

На фиг. 1 показана принципиальная электрическая схема запоминающего устройства емкостью 16 бит; на фиг. 2 — характеристика перезаписи МДП-транзистора с изменяемым пороговым напряжением.

Предлагаемое запоминающее устройство выполнено на одном полупроводниковом кри5 сталле. Оно содержит матрицу накопителя па

МДП-транзисторах 1 — 16 с изменяемым пороговым напряжением, например р-канальных

МНОП-транзисторах. Матрица на кристалле 1 размещена в изолированном кармане 17 и име1о ет выход 18 от подложки. Дешифратор столбцов матрицы состоит из четырех двухвходовых логических ячеек «HE — ИЛИ», содержащих нагрузочные 19 — 22 и активные 23 — 30 транзисторы. Нагрузочные транзисторы подключеI5 ны к шине питания 31, а активные — к шине

32. Истоковые шины каждого из столбцов через управляющие транзистора 33 — 36 связаны с шиной 37 питания матрицы, а через дополнительные управляющие транзисторы 38 — 41—

20 с выходными шинами дешифратора столбцов и затворам транзисторов 33 — 36. Транзисторы 38 — 41 имеют общую затворимую шину 42.

Стоковые шины каждого из столбцов подключены через транзисторы 43 — 46, объединенные

25 по затворам шиной 47, к шине считывания 48.

Дешифратор столбцов и управляющие транзисторы находятся в изолированном кармане

49, имеющем вывод 50 от подложки, Дешифратор 51 строк, аналогичный дешифратору

33 столбцов, также размещен в изолированном

3 кармане 52, имеющем вывод 53 от подло?кки.

МДП-транзисторы дешифраторов и все управляющие транзисторы имеют тот же тип проводимости, что и транзисторы накопителя т. е. р-канальные 1 ь У, У, ) и Хь Хь Х, Х вЂ” адресные входы дешифраторов строк и столбцов соответственно.

Устройство работает следу!ощим образом.

У МНОП-транзисторов с изменяемым пороговым напряжением характеристики перезапу!си, представляющая собой зависимость величины порогового напряжения U от амплитуды напряжения на подзатворном диэлектрике при достаточно большой его длительности (например, 10 мсек) имеет вид петли гистерезиса (фиг. 2). Значениям +U, и — U,.„соответствуют сохраняющиеся продолжительное время величины пороговых напряжений Uо и U .Величина U о в зависимости от конструкции и технологии изготовления МНОП-транзистора может быть положительной (кривая А) либо отрицательной (кривая Б), но как правило,— отрицательная. Для нормальной работы необходимо, чтобы (+ /у.) = (— К.УΠ— (+ Uy.) = — — (— Uy )

1 1 что обычно имеет место при (Uy„) 30в (Уу„) — 50в.

Стирание информации в матрице, как обычно, осуществляют подачей импульса +U,,„„íà выходе 18 подложки после отключения источников питания. При этом пороговые напряжения U, всех транзисторов матрицы становятся равными U,ò, е. каждый транзистор матрицы переходйт в логическое состояние «1», Выборочную запись, например, в транзистор 1 матрицы осуществляют следующим образом.

Выводы 32, 48, 53 шин и подложки заземляют, на выходы 18 и 50 и шины 37, 47 и 31 подают положительное напряжение !/ U„, на шину

42 — отрицательное напряжение, обеспечивающее отпирание транзисторов 38 — 41. На входы Уь 1 ь У . У и Хь Х, Х, Х! дешифраторов подают код адреса МДП-транзистора 1, так что в дешифраторе столбцов (в дешифраторе строк — аналогично) транзисторы 23 и 24 закрыты, а хотя .бы один в каждой из пар транзисторов 25 — 26, 27 — 28, 29 — 30 открыт. Таким образом выбранный столбец матрицы, т. е. его истоковая и стоковая шины, оказываются изолированным от заземленного вывода шины 32, а истоковые шины всех остальных (невыбранных) столбцов заземлены через открытые транзисторы 25 — 30, 39 — 41.

На шину питания дешифратора 51 строк подают отрицательный импульс напряжения величиной около (!/ (— U,,) — ) в и длительностью 300 — 600 мсек. При этом на шине затворов выбранной строки появляется отрицательный импульс с амплитудой около >/> !/у, а на шинах затворов остальных (невыбранных) строк — около 0 в. Во время действия этого

479153 отрицательного имп).лиса под затворами транзисторов 1 — 4 образуются р-каналы. При этом р-каналы транзисторов 3 — 4 оказываются заземленными по истоковым шинам, а р-канал

5 транзистора 1 изолирован от заземленной шины. Поэтому во время действия импульса к подзатворному диэлектрику транзистора 1 прило?кено напря?кение величиной

1 1

10 (ун) + 2 (ун) — ун а к подзатвор ым диэлектрикам остальных транзисторов матрицы — не более !/ U; .

Это приводит к тому, что величина порогового

15 напряжения транзистора 1 становится равной

Uo, пороговые напряжения остальных транзисторов матрицы остаются прежними и рав.Л ными U,т. е. только выбранный транзистор 1 переходит в логическое состояние «О».

Выборочное считывание осуществляют следующим образом.

Выводы шин 32, 42 и выводы подложек 50 и

53 заземляют, На выводы шины 37 и подложки 18 подают отртщательное напряжение — (U ) +2 в, если U )О, и заземляют их, если !/+(О. Это обеспечивает смещение характеристики перезаписи в область отрицательных значений пороговых напряжений.

На выводы шин 31 и 47 подают напряжение — 20 в, что обеспечивает отпирание транзисторов 19 — 22 и 43 — 46. На вывод шины 48 подают отрицательное напряжение — (1/о )+

+6 в, вследствие чего разность потенциалов между выводами шин 37 и 48 равна — 4 в.

При такой комбинации потенциалов дополнительные управляющие транзисторы 38 — 41 заперты. Напряжение питания дешифратора 51

4р строк дол?Кно cocTBÂëÿòü (Uo ) (/о ) — 6в.

Благодаря этому обеспечивается на затворной

45 шине выбранной строки наличие отрицательного потеп циала, приблизительно равного по величине среднему. значению между Uo u Uo.

При наличии на входах дешифраторов кода адреса, например, транзистора 1, на затворной

50 шине верхней строки потенциал равен (1/о ) — (Uо ) — 2в, 2 а для остальных строк — около 0 в. При этом

55 транзисторы 23 и 24 закрыты, а хотя бы один из транзисторов 25 — 30 открыт. Это значит, что транзистор 33 открыт, а транзисторы

34 — 36 закрыты, по цепи: вывод шины 37— транзисторы 33, 1, 43 — вывод шины 48 про60 текает ток, если МДП-транзистор 1 находится в состоянии логической «1», и ток отсутствует, если он находится в состоянии логического

«О». В цепях всех невыбранных столбцов ток не .протекает, так как транзистооы 34 — 36 за65 перты.

479153

Итак, предлагаемая схема инвариантна к виду характеристики перезаписи МДП-транзистора, так как для се работы достагочно измерить значения U и U характеристики перезаписи и выбрать по указанным выше формулам величины напряжений источников питания, не изменяя самой схемы устройства.

Предмет изобретения

Интегральное запоминающее устройство, содержащее матрицу накопителя на МДПтранзисторах с изменяемым пороговым напряжением, дешифраторы строк и столбцов и управляющие транзисторы, соединяющие шины столбцов накопителя с выходной шиной дешифратора, отличающееся тем, что, с целью улучшения эксплуатационных характеристик и технологичности запоминающего устройства, оно содержит дополнительные управляющие транзисторы, затворы которых под10 ключены к шине управляющего сигнала, стоки подключены к выходным шинам дешифратора столбцов, а истоки — к шинам столбцов матрицы накопителя.

479153

/jïàð

Фиг 2

Составитель Р. Яворовская

Техред Л, Казачкова Корректор T. Добровольская

Редактор Т. Рыбалова

Типография, пр. Сапунова, 2

Заказ 2511/20 Изд. № 1677 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5