Дисретная линия задержки

Иллюстрации

Показать всеРеферат

1 (ii) 479233

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 27.03.72 (21) 1762871/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.75. Бюллетень № 28

Дата опубликования описания 16.10.75 (51) М. Кл. Н 03k 5/13

Государственный комитет

Совета Министров СССР ло делам изобретений н открытий (53) УДК 621.374.5 (088.8) (72) Авторы изобретения

В. В. Меркуль и И. Л. Перельман (71) Заявитель Информационно-вычислительный центр Министерства промышленного строительства Белорусской ССР (54) ДИСКРЕТНАЯ ЛИНИЯ ЗАДЕРЖКИ

Изобретение относится к радиотехнике и может быть использовано в устройствах с переменной временной последовательностью сигналов.

Известна дискретная линия задержки, содержащая триггер Шмитта, к выходу которого через дифференцирующую цепь подключен один из входов триггера пуска, многовходовой дешифратор кода условий с и выходами, к каждому из которых подключен диод и многозвенная резистивная цепь, включенная в общую цепь обоих эмиттеров транзисторов триггера Шмитта.

Однако известное устройство обладает низкой точностью дискретного изменения времени задержки.

Целью изобретения является увеличение точности дискретного изменения времени задержки устройства.

Для этого к входу триггера Шмитта дополнительно подключен интегрирующий конденсатор, времязадающий резистор и коллектор транзистора разряда интегрирующего конденсатора, к базе которого через резистор подключен выход триггера пуска, при этом выходы многовходового дешифратор а кода условий соединены через диоды с соответствующими резисторами многозвенной резистивной цепи.

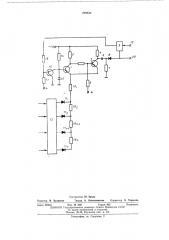

На чертеже показана принципиальная электрическая схема устройства.

Дискретная линия задержки содержит

5 триггер Шмитта на транзисторах 1, 2 и резисторах 3, 4, 5. К выходу триггера Шмитта через дифференцирующую цепь из конденсатора 6, резистора 7 и диода 8 подключен один из входов триггера 9 пуска. Б эмиттерную

1о цепь транзисторов 1, 2 включена многозвенная резистивная цепь, состоящая из резисторов 10 (10т — 10 ), к которой через диоды 11 (111 — 11„) подключены выходы дешифратора 12.

К входу триггера Шмитта подключен интегрирующий конденсатор 13, времязадающий резистор 14 и коллектор транзистора 15 разряда интегрирующего конденсатора 13. К базе транзистора 15 через резистор 16 подключен выход триггера 9 пуска. Через резисторы 5 и 17 на базы транзисторов 2 и 15 подается положительное смещение.

На клемму 18 подается питание. На клемму 19 подаются импульсы пуска. С выходной клеммы 20 снимаются задержанные импульсы.

Дискретная линия задержки работает сле3Q дующим образом

Если в начальный момент триггер 9 находится в состоянии «нуль», то на базу транзистора 15 через резистор 16 поступает отрицательный потенциал. Транзистор 15 находится в насыщении и заряд на конденсаторе 13 отсутствует. Транзистор 1 триггера Шмитта закрыт, а транзистор 2 — открыт и на его эмиттере присутствует потенциал, соответствующий коду условий.

При поступлении на входную клемму 19 пускового импульса триггер 9 переходит в

«единичное» состояние и закрывает транзитор 15, Конденсатор 13 начинает заряжаться до напряжения, соответствующего коду условий.

По достижении напряжения на конденсаторе

13 величины, соответствующей коду условий, триггер Шмитта перебрасывается.

Импульс от триггера Шмитта подается на нулевой вход триггера 9 через дифференцирующую цепь, состоящую из конденсатора 6, резистора 7 и диода 8. При этом триггер 9 перебрасывается в «нулевое» положение.

479233

Предмет изобретения

Дискретная линия задержки, содержащая триггер Шмитта, к выходу которого через

5 дифференцирующую цепь подключен один из входов триггера пуска, многовходовой дешифратор кода условий с и выходами, к каждому из которых подключен диод и многозвенная резистивная цепь, включенная в обlo щую цепь обоих эмиттеров транзисторов триггера Шмитта, отличающаяся тем, что, с целью увеличения точности дискретного изменения времени задержки, к входу триггера

Шмитта дополнительно подключен интегриру15 ющий конденсатор, времязадающий резистор и коллектор транзистора разряда интегрирующего конденсатора, к базе которого через резистор подключен выход триггера пуска, прн этом выходы многовходового дешифратор а

20 кода условий соединены через диоды с соответствующими резисторами многозвенной резистивной цепи.

479233

Составитель Ю. Юркин

Редактор В. Булдаков Техред A. Камышникова Корректор 3. Тарасова

Заказ 2502 9 Изд. № 1667 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2