Устройство для кодирования и декодирования информации

Иллюстрации

Показать всеРеферат

(») 480074

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик.(61) Зависимое от авт. свидетельства (22) Заявлено 26.05.72 (21) 1796070/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 05.08.75. Бюллетень № 29

Дата опубликования описания 28.11.75 (51) M. Кл. б 06f 5/00

Государственный комитет

Совета Министров СССР по делам изобретений и откоытнй (53) УДК 681.326(088.8) (72) Авторы изоорстсння

В. Ф. Корнеев и H. Б. Тарасенко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ

ИНФОРМАЦИИ

Изобретение относится к области управления движущимися объектами и может оыть использовано в специальных устройствах, например, для бортовых систем.

Известны устройства для кодирования и декодирования информации, содержащие цепь последовательно включенных элементов задержки, выходы которых подключены к соответствующим входам выходных элементов

«И» и «ИЛИ», и согласующий каскад, вход которого подключен ко входу кодирования устройства.

Во всех известных устройствах требуется применение раздельных схем для выполнения операций кодирования и декодирования, что обуславливает значительные габариты устройства и невысокую надежность работы.

В предложенном устройстве эти недостатки устр анены.

Устройство отличается от известных тем, что оно содержит схему запрета, входы которой подключены к выходу согласующего каскада и входу декодирования устройства, а выход — ко входу цепи элементов задержки.

Схема запрета выполнена на двух параллельно соединенных транзисторах одного типа проводимости, включенных по схеме эмиттерного повторителя. Согласующий каскад содержит два последовательно включенных транзистора различного типа проводимости.

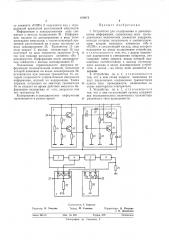

Схема устройства для кодирования и декодирования информации приведена на чертеже.

Устройство содержит согласующий каскад

5 1, схему запрета 2, элементы задержки 3 — 6, выходной элемент «И» 7 и выходной элемент

«ИЛИ» 8.

Согласующий каскад 1 содержит последовательно включенные транзисторы 9 и 10 раз10 ного типа проводимости и резисторы ll — 14.

Схема запрета 2 содержит два параллельно соединенных транзистора 15 и 16 одного типа проводимости, резисторы 17 — 20, диод 21 и конденсаторы 22 и 23. Последовательно вклю15 ченные элементы задержки 3 — 6 соединены с согласующим резистором 24.

Выходной элемент «ИЛИ» содержит диоды

25 — 27 и резистор 28, выходной элемент «И»вЂ” диоды 29 — 31, резистор 32 и клемму 33, к ко20 торой подводится положительный потенциал.

Устройство работает следующим образом.

Информация, идущая на кодирование в виде отрицательных импульсов, поступает на

2ь вход кодирования 34. При этом отрицательные импульсы открывают транзистор 10, который был закрыт, так как на его базу подается небольшое отрицательное смещение относительно эмиттера, и проходят на цепь элемен30 тов задержки 3 — 6, где при помощи выходноСоставитель Г. Сорокин

Техред M. Семенов

Корректоры: В. Петрова и О. Данишева

Редактор Л. Утехина

Изд. № 933

Заказ 2914/5

Тираж 679

Подписное

Типография, пр. Сапунова, 2 го элемента «ИЛИ» 8 получается код с определенной временной расстановкой импульсов.

Информация в закодированном виде снимается с выхода кодирования 35. Информация, идущая на декодирование в виде положительных импульсов, с соответствующей временной расстановкой их в коде, поступает на вход декодирования 36. Транзистор 15 при этом закрыт. С выхода транзистора 16 код поступает на цепь элементов задержки 3 — 6, где при помощи выходного элемента «И» 7 декодируется. Информация после декодирования снимается с выхода декодирования 37.

Подавление отрицательного импульса информации положительной помехой, появление которой возможно на входе декодирования 36, исключается при помощи транзистора 15, который открывается отрицательным импульсом информации, идущей на кодирование. Таким образом, потенциал на эмиттере транзистора

16 не спадает во время действия импульса информации независимо от того, закроется или нет транзистор 16.

Кодирование и декодирование информации производится в разное время.

Предмет изобретения

1. Устройство для кодирования и декодирования информации, содержащее цепь после5 довательно включенных элементов задержки, выходы которых подключены к соответствующим входам выходных элементов «И» и

«ИЛИ», и согласующий каскад, вход которого подключен ко входу кодирования устройства, 10 отличающееся тем, что, с целью повышения надежности и уменьшения габаритов, оно содержит схему запрета, входы которой подключены соответственно к выходу согласующего каскада и входу декодирования устрой15 ства, а выход — ко входу цепи элементов задержки.

2, Устройство по п. 1, отличающееся тем, что в нем схема запрета выполнена на двух параллельно соединенных транзисторах

20 одного типа проводимости, включенных по схеме эмиттерного повторителя.

3. У строй ство по п. 1, о т л и ч а ю щ е е с я тем, что в нем согласующий каскад содержит два последовательно включенных транзистора

25 различного типа проводимости.