Устройство для умножения

Иллюстрации

Показать всеРеферат

О П И С А Н И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Социалистических

Республик (б1) Зависимое от авт. свидетельства (22) Заявлено 04.07.73 (21) 1938722/18-24 с присоединением заявки №

ГосУдаРстввнный комитет (32) 11риоритет

Совета Министров СССР по делам изобретений Опубликовано 05.08.75. Бюллетень № 29 (51) М. Кл. G 06g 7/16 (53) УДК 681.335(088.8) и открытий

Дата опубликования описания 11.03.7б (72) Авторы изобретения

И. И. Смилянский, Е. В. Корсунова и Л. А. Яновский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНО)КЕНИЯ

Изобретение относится к вычислительной технике и может быть применено в аналоговых вычислительных машинах, в приборах и устройствах автоматики для получения произведения двух электрических сигналов.

Известно устройство для умножения, содержащее два источника входных сигналов, интегратор, вход которого подключен к первому источнику входного сигнала, и компаратор, первый вход которого соединен с выходом интегратора, а второй — со вторым источником входного сигнала.

Однако такие устройства требуют наличия схемы, генерирующей f (), установки одних и тех же начальных условий, связанной с введением дополнительных ключей, и наличия второго канала. Это понижает надежность устройства, увеличивает количество оборудования, стоимость и габариты устройства.

С целью упрощения устройства выход компаратора подключен ко входу интегратора и к управляющему входу дополнительно введенного фазочувствительного выпрямителя, вход питания которого подключен к выходу интегратора, а выход — к выходу устройства.

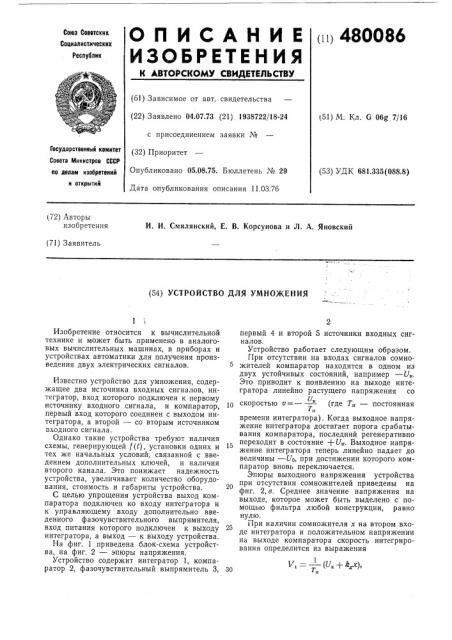

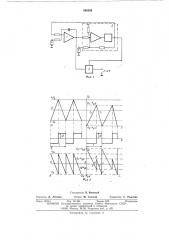

На фиг. 1 приведена блок-схема устройства, на фиг. 2 — эпюры напряжения.

Устройство содержит интегратор 1, компаратор 2, фазочувствительный выпрямитель 3, первый 4 и второй 5 источники входных сигналов.

Устройство работает следующим образом.

При отсутствии на входах сигналов сомножителей компаратор находится в одном из двух устойчивых состояний, например — U„, Это приводит к появлению на выходе интегратора линейно растущего напряжения со ти скоростью v =— (где Т„ — постоянная ти времени интегратора). Когда выходное напряжение интегратора достигает порога срабатывания компаратора, последний регенеративно переходит в состояние +У„. Выходное напряжение интегратора теперь линейно падает до величины — Uo, при достижении которого компаратор вновь переключается.

Эпюры выходного напряжения устройства при отсутствии сомножителей приведены на фиг. 2, в. Среднее значение напряжения на выходе, которое может быть выделено с помощью фильтра любой конструкции, равно нулю.

11ри наличии сомножителя х на втором входе интегратора и положительном напряжении на выходе компаратора скорость интегрирования определится из выражения т

480086 а при отрицательном напряжении на выходе компаратора

V,= — (— U,+А х), г„

Если при этом на второй вход компаратора подан сигнал второго сомножителя +у, то при положительном напряжении на выходе компаратора порог срабатывания последнего равен 1 (о + >ó Ó а при отрицательном напряжении на выходе компаратора я: о+ уУ

Эпюры выходных напряжений на выходах интегратора, компаратора и фазочувствительного выпрямителя для этого случая приведены на фиг. 2, г, д, ж соответственно.

Длительность положительного импульса на выходе компаратора определяется выражением

У вЂ” У2 2УО Ти

Ук+ л х а.длительность отрицательного импульса

Ук — Ug 2Уо Ти

Vs Ук хх

Период напряжения на выходе компаратора и соответственно на выходе устройства равен у g 4УоУкли

У хг

Среднее значение напряжения на выходе фазочувствительного выпрямителя равно отношению алгебраической суммы площадей треугольников ОАВ, ВСН, HDE и ЕР1 (фиг.

2, ж) к периоду генерируемого напряжения.

Высоты треугольников равны порогам срабатывания U> и U2 компаратора, а основания определяются временами интегрирования от соответствующего уровня до нуля со скоростью V> или Vz в зависимости от полярности напряжения на выходе компаратора, где

Г

V2 = — Uq, так как при — Ук выходной сигнал интегратора инвертируется фазочувствительным выпрямителем.

Таким образом, среднее значение выходного напряжения устройства определяется выра,О жением

У„й,х T„(U,+А у)

TH (Up+Ay у) Tg (Up k> у) 2 (Ук — /гх х) 2 (Ук + P, х) +

T„(— У„-)- /гав у) Й А

2 (Uê+ / х х) ) У„

ЗО

Предмет изобретения

Устройство для умножения, содержащее два источника входных сигналов, интегратор, вход которого подключен к первому источнику входного сигнала, и компаратор, первый вход которого соединен с выходом интегратора, а второй — со вторым источником входного сигнала, отличающееся тем, что, с целью упрощения устройства, выход компаратора

4о подключен ко входу интегратора и к управляющему входу дополнительно введенного фазочувствительного выпрямителя, вход питания которого подключен к выходу интегратора, а выход — к выходу устройства.

Следовательно, среднее значение напряже2О ния на выходе устройства пропорционально произведению входных сигналов и его знак определяется соотношением знаков сомножителей.

Таким образом, предложенное устройство позволяет получить четырехквадрантное перемножение входных сигналов, при более простой, IIO сравнению с известными устройствами, схеме соединения.

480086

< о уу

4 и2. 2

Составитель Л. Яновский

Техред М. Семенов

Корректор Е. Рожкова

Редактор Л. Утехина

Типография, пр. Сапунова, 2

Заказ 122/14 Изд. ¹ 934 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5