Интерполятор

Иллюстрации

Показать всеРеферат

1 ;КАЯ

O ll И -М-й"

ИЗОБРЕтЕНИя

4воои

Союэ Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 08.08.73 (21) 1955730/18-24 (51) М. Кл. G 06k 7j10 с присоединением заявки ¹â€”

Государственный квмитет

Совета Министров СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 05,08.75. Бюллетень - 29

Дата опубликования описания 13.04.76 (53) УДК 681.335.87 (088.8) (72) Лвторы изобретения

В. Н. Коробейников и А. Ф. Кургаев

Ордена Ленина институт кибернетики AH УССР (71) Заявитель (54) И НТЕРПОЛЯТОР

Изобретение относится к вычислительной технике и может быть использовано для воспроизведения функций, зависящих от времени, при выводе информации на электроннолучевые трубки, графопостроители и исполнительные механизмы в управляющих вычислительных системах.

Известен интерполятор, содержащий цепочки, выполненные в виде последовательно соединенных сумматора, ключа, аналогового запоминающего устройства и интегратора, выход которого подключен к одному из входов сумматора.

Известный интерполятор характеризуется низкой точностью воспроизведения функциональных зависимостей.

Цель изобретения — повышение точности интерполяции.

Указанная цель достигается тем, что в предлагаемом интерполяторе входы сумматора каждой последующей цепочки подключены соответственно к выходам сумматора и аналогового запоминающего устройства предыдущей цепочки, один из входов интегратора которой подключении к выходу интегратора последующей цепочки, другие входы интеграторов каждой из цепочек подключены к выходам аналоговых запоминающих устройств всех последующих цепочек, а между входами и выходами интеграторов всех цепочек, кроме первой, установлены дополнительные ключи.

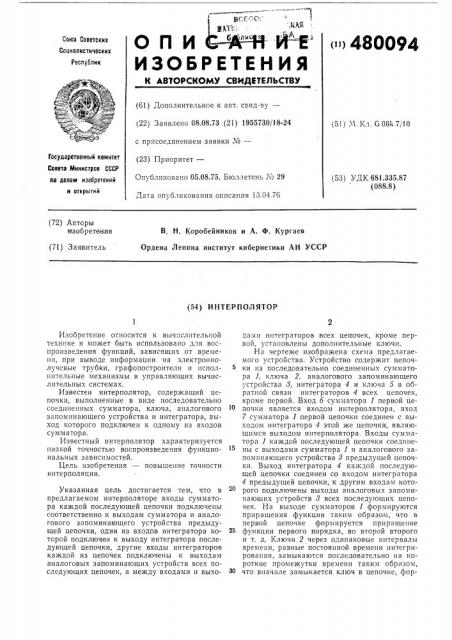

На чертеже изображена схема предлагаемого устройства. Устройство содержит цепочки из последовательно соединенных сумматора 1, ключа 2, аналогового запоминающего устройства 3, интегратора 4 и ключа 5 в обратной связи интеграторов 4 всех цепочек, кроме первой. Вход б сумматора 1 первой цепочки является входом интерполятора, вход

7 сумматора 1 первой цепочки соединен с выходом интегратора 4 этой же цепочки, являющимся выходом интерполятора. Входы сумматора 1 каждой последующей цепочки соединены с выходами сумматора 1 и аналогового запоминающего устройства 8 предыдущей цепочки. Выход интегратора 4 каждой последующей цепочки соединен со входом интегратора

4 предыдущей цепочки, к другим входам которого подключены выходы аналоговых запоминающих устройств 8 всех последующих цепочек. На выходе сумматоров 1 формируются приращения функции таким образом, что в первой цепочке формируется приращение

25 функции первого порядка, во второй второго и т. д. Ключи 2 через одинаковые интервалы времени, равные постоянной времени интегрирования, замыкаются последовательно на короткие промежутки времени таким образом, зО что вначале замыкается ключ в цепочке, фор5 и

Зо

55 б0

65 мирующей и интегрирующей приращение максимального порядка, после его размыкания замыкается ключ 2 предыдущей цепочки и т. д. Ключи 5 замыкаются одновременно на короткие промежутки времени в начале цикла интегрирования.

Интерполятор работает следующим образом.

На вход интерполятора поступает ступенчатое напряжение. Длительности ступенек напряжения одинаковы и равны постоянной времени интегрирования интеграторов 4, а величина каждой ступеньки равна значению интерполируемой функции в тот момент времени, в который начинается эта ступенька. На вход 7 сумматора 1, стоящего на входе интерполятора, поступает напряжение обратной связи с выхода интерполятора.

В начальный момент времени замыкаются ключи 5 и на выходах соответствующих интеграторов 4 устанавливается напряжение, равное нулю. Затем замыкается ключ 2 в цепочке, формирующей и интегрирующей разность максимального порядка. Инверсная сумма (с учетом знаков) напряжений на входах 6 и 7 с выхода сумматора 1 первой цепочки иптерполятора (прирашение функции первого порядка) поступает па один из входов сумматора 1 следующей цепочки, на второй вход которого поступает напряжение с выхода аналогового запоминающего устройства 8 первой цепочки интерполятора. Инверсная сумма (с учетом знаков) напряжений на входах сумматора 1 второй цепочки интерполятора (приращение функции второго порядка) с выхода сумматора 1 этой цепочки поступает на один из входов сумматора 1 следующей цепочки, на второй вход которого поступает напряжение с выхода аналогового запоминающего устройства 8 второй цепочки интерполятора и т. д. до формирования приращения функции а-го порядка, которая с выхода соответствующего сумматора 1 через открытый ключ 2 поступает на вход соответствующего аналогового запоминающего устройства 8 и запоминается

ELB нем. Затем ключ 2 в этой цепочке размыкается и замыкается ключ 2 в предыдущей цепочке. Приращение функции (n — 1)-го порядка с выхода соответствующего сумматора

1 запоминается в соответствующем аналоговом запоминающем устройстве. Ключ 2 в этой цепочке размыкается и т. д. Приращения функции всех порядков (с п-го по первый) запоминаются последовательно в соответствующих аналоговых запоминающих устройствах

8, причем все приращения функции нечетного порядка запоминаются в аналоговых запоминающих устройствах 8 с истинным знаком, а четного порядка — с инверсным. Затем начинается цикл интегрирования (собственно интерполяций).

Интегратор 4, стоящий в цгпоч ::, фор:..::руюшей приращение функции максимального порядка (n-го), интегрирует только это приращение. Интегратор 4, стоящий в предыдущей цепочке, т. е. в той цепочке, в которой формируется приращение функции (п — 1) -го порядка, интегрирует сумму напряжений (с учетом их знаков), состоящую из: напряжения с выхода аналогового запоминающего устройства 8 этой цепочки, напряжения с выхода аналогового запоминающего устройства

8 и напряжения с выхода интегратора 4 последующей цепочки.

Аналогичным образом интегратор 4, стоящий в произвольной цепочке, интегрирует сумму напряжений (с учетом их знаков), состоящую из: напряжения с выхода аналогового запоминающего устройства 8 этой цепочки, напряжения с выхода интегратора 4 последующей цепочки и напряжений с выходов аналоговых запоминающих устройств 8 всех последующих цепочек. Напряжения с выходов аналоговых запоминаюшпх устройств

8 всех цепочек передаются на входы интеграторов 4 этих же цепочек с коэффициентами, равными 1, а на входы интеграторов 4 предыдущих цепочек — с коэффициентами, меньшими 1, Их величины определяются из интерполяциовного полинома Ньютона.

Выходное напряжение интерполятора и(/) при этом является функцией времени t и определяется выражением где T — постоянная времени интеграторов 4;

Наличие отрицательной обратной связи, позволяет избежать накапливания ошибок, образующихся в результате нестабильности коэффициентов передач элементов интерполятора и рассогласования постоянных времен интегрирования и интервалов интерполяции.

Предмет изобретения

Интерполятор, содержащий цепочки, каждая из которых выполнена в виде последовательно соединенных сумматора, ключа, аналогового запоминающего устройства и интегратора, в одной из цепочек выход интегратора подключен к одному из входов сумматора, отличаюи1ийся тем, что, с целью повышения точности работы, входы сумматора каждой последующей цепочки подключены соответственно к выходам сумматора и аналогового запоминающего устройства предыдущей цепочки, один из входов интегратора которой подключен к выходу интегратора последующей цепочки, другие входы интеграторов каждой из цепочек подключены к выходам аналоговых запоминающих устройств всех последующих цепочек, а между входами и выходами интеграторов каждой цепочки, кроме первой, установлены дополнительные ключи.

48ОО94

Редактор Н. Вирко

Корректор В. Гутман

Заказ 164/339 Изд. М 5 Тираж 679 По:пнсное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»

Г

I !

Составитель В. Киселев

Техред Т. Миронова