Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

...3- !/ . -.:: -г, 1. . ь к .;

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ й11 480 I 76

Сова Севетскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 07.12.72 (21) 1854765/26-9 с присоединением заявки _#_å (23) Приоритет

Опубликовано 05.08,75. Бюллстепь М 29

Дата опубликования описания 16.01.76 (51) М. Кл. Н 03f 3/34

Государстеслиый комитет

Совета Министров СССР ло делам изобретеиий и 07KpblTHN (53) УДК 62!.375.024 (088.8) (72) Лвторы изобретения

В. В. Макашин и В. В. Каминский (71) Заявитель (54) ДИФФЕРЕНЦИАЛЬНЬ!Й УСИЛИТЕЛЬ

Изобретение относится к радиотехнике, может использоваться в качестве операционного усилителя в измерительной и вычислительной технике.

Известен дифференциальный усилитель, содержащий последовательно соединенные входной и выходной дифференциальные каскады и цепь отрицательной обратной связи на повторителе напряжения.

Цель изобретения — повышение стабильности коэффициента усиления.

Предлагаемый усилитель отличается тем, что в цепи эмиттеров транзисторов входного каскада введены резисторы, а между коллектором транзистора одного плеча выходного каскада и эмиттером транзистора соответствующего плеча входного каскада введена упомянутая цепь отрицательной обратной связи; при этом между коллектором транзистора другого плсча выходного каскада и эмиттером транзистора соответствую.цего плеча входного каскада включена аналогичная цепь отрицательной обратной связи.

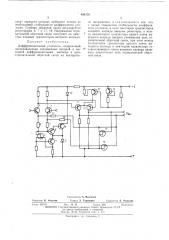

На чертеже изображена схема дифференциального усилителя.

Дифференциальный усилитель состоит из входного и выходного дифференциальных каскадов, генератора тока и cocTAB|10I эмиттерного повторителя. Входной каскад выполпен па транзисторах 1, 2 по дифференциальной схеме с симметричными входом и выходо ll.

Генератор тока, состоящий из транзисторов 3, 4, стабилитрона 5, соединен с эмиттерами транзисторов 1, 2 через резисторы 6 и 7.

Эмиттерный повторитель состоит из транзисторов 8, 9; выход последнего через стабилитрон 10 подключен к источнику питания.

Выходной каскад выполнен на транзпсто рах 11, 12 по дифференциальной схеме с симметричными входом и вь.ходом, генератором тока в цепи эмпттера, собр.-.пном па транзисторах 13, 14.

Коллекторы транзисторов 11, 12 через повторители напряжения на транзисторах 15, 16

15 и резисторы 17, 18 соединены с эмиттерамп транзисторов 1, 2 входного каскада, а базы транзисторов 11, 12 подключены к коллекторам транзисторов 1, 2 входного каскада соответственно.

20 Повторители напряжения совместно с резисторами 6, 7 образуют цепь последовательной отрицательной связи по напряжению для разяофазного (дифференциального) сипнала.

Работает устройство следующим образом.

25 Входной сигнал поступает на базы транзисторов 1 и 2. Усиленный разнофазный сигнал снимается с коллекторов этих транзисторов и поступает на базы транзисторов 1, 12 выходного каскада, Выходной сигнал по"тупает на

ЗО входы повторителей напряжения, коэффи480!76

Составитель А. Максаков

Техред 3. Тараиеико

Редактор Б. Федотов

Корректор Е. Рожкова

Заказ 3225, 3 Изд. № 29 . Тираж 902 Подписное

ЦИИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

Москва, Я-35, Раугиская tIHo., д. 4/5

Типографии, ир, Сапунова, 2 циент передачи которых выбирают исходя из необходимой стабильности коэффициента усиления. Глубина обратной связи регулируется резисторами 6, 7 и 17, 18. Напряжение отрицательной обратной связи поступает на эмиттеры входных транзисторов входного каскада.

Предмет изобретения

Дифференциальный усилитель, содержащий последовательно соединенные входной и выходной дифференциальные каскады и цепь отрицательной обратной связи на повторителе напряжения, отличающийся тем, что, с целью повышения стабильности коэффициента усиления, в цепи эмиттеров транзисторов входного каскада введены резисторы, а между коллектором транзистора одного плеча выходного каскада введена упомянутая цепь отрицательной обратной связи, при этом между коллектором транзистора другого плеча выходного каскада и эмиттером транзистора соответствующего плеча входного каскада включена аналогичная цепь отрицательной обратной связи.