Делитель частоты на потенциальных элементах

Иллюстрации

Показать всеРеферат

ОПИС

ИЗОБРЕ

К АВТОРСКОМУ

Сова Советских

Ьодиалистических

Республик

{61) Дополнительное к (22) Заявлено 30.03.71 с присоединением (23) Приоритет

Опубликовано 05.08.75.

Дата опубликования о

Государственный комитет

Сове1а Министров СССР но делам изобретений и открытий (72) Авторы изобретения

P. В. Багдасарова и Г. Л. Рубинштейн (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ НА ПОТЕНЦИАЛЬНЫХ ЭЛЕМЕНТАХ

Предмет изобретения

Изобретение относится к импульсной технике.

Известен делитель частоты на потенциальных элементах, каждый разряд которого содержит шесть многовходовых элементов

«И — HF/ИЛИ вЂ” HE», образующих три статических триггера с раздельными входами.

Нулевые выходы второго и третьего триггеров соединены соответственно с нулевым и единичным входами первого триггера, единичные выходы первого и второго триггеров соединены соответственно с нулевыми входами второго и третьего триггеров, нулевой выход третьего триггера соединен с единичным входом второго.

Цель изобретения — получение любого целочисленного коэффициента деления.

Предлагаемый делитель частоты отличается тем, что в него введена схема совпадения, входы которой соединены с единичными выходами третьих триггеров всех разрядов, а выход схемы совпадения соединен со входами многовходовых элементов «И вЂ” НЕ/ИЛИ—

НЕ» нулевых плеч третьих триггеров соответствующих разрядов.

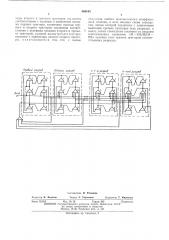

На чертеже представлена схема устройства.

Делитель содержит счетные триггеры на потенциальных многовходовых элементах

«И — HE/ИЛИ вЂ” НЕ» 1 — 6, схему совпадения 7.

Делитель частоты на потенциальных элементах представляет собой счетчик, работающий от вписанного числа 2" — к до переполнения, где к — коэффициент деления, и — коли5 честно разрядов.

Пусть в исходном состоянии в счетчик записано число 2" — к, Тогда после прихода к—

1-го счетного импульса счетчик переполпяется (все разряды устанавливаются в состояние

10 «единица»), и на выходе схемы совпадения формируется запрещающий потенциал, во времени расположенный между задними фронтами к — 1 и к-го импульсов, т.е. перекрывающий временное положение к-го импульса.

15 После прихода к-го импульса те разряды делителя, к которым подключен выход схемы совпадения 7, остаются в единичном состоянии, а остальные переводятся в нулевое состояние, и в счетчик записывается число 2" — к.

20 Таким образом, делитель возвращается в исходное состояние. После этого цикл его работы повторяется.

Делитель частоты на потенциальных элементах, каждый разряд которого содержит шесть многовходовых элементов «И вЂ” НЕ/

ИЛИ вЂ” НЕ», образующих три статических

30 триггера с раздельными входами, нулевые вы480)93

Первый разряа

Втораи разряд

n -u разряа а - нь и разряд

Составитель И. Разинова

Текред 3. Тараненко

Корректор Т. Миронова

Редактор Б. Федотов

Заказ 3215/6 Изд. № 30 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открь!тий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ходы второ;о и ретьего триггеров соединены соответственно с нулевым и единичным входами первого триггера, единичные выходы первого и второго триггеров соединены соответственно с нулевыми входами второго и третьего триггеров, нулевой выходтрстьеготрпггера соединен с единичным входом второго триггера, отличающийся тем, что, с целью получения любого целочисленного коэффициента деления, в него введена схема совпадения, входы которой соединены с единичными выходами третьих триггеров всех разрядов, а выход схемы совпадения соединен со входами многовходовых элементов «И вЂ” НЕ/ИЛИ—

НЕ» нулевых плеч третьих триггеров соответствующих разрядов.