Вычислительное устройство для индикатора истинного движения судовой радиолокационной станции

Иллюстрации

Показать всеРеферат

О П И С А Н И=В

ИЗОБРЕТЕНИЯ

Р11 48IO 50

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 02.03.73 (21) 1889373 18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.08.75. Б1о I,ëcòñíü ¹ 30

Дата опубликования описания 22.01.76 (51) М. Кл. G 06g 7i 78

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.34(088.8) (72) Автор изобретения

Л. С. Бельцер (71) Заявитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ИНДИКАТОРА

ИСТИННОГО ДВИ)КЕНИЯ СУДОВОЙ РАДИОЛОКАЦИОННОЙ

СТАНЦИИ

Предлагаемое устройство относится к области вычислительной техники и может быть использовано в навигационных радиолокационных станциях.

Известны вычислительные устройства для индикатора истинного движения судовой радиолокационной станции, содержащие датчик скорости, смещающую катушку индикатора, координатор, два интегрирующих привода с установленными на выходных валах датчиками текущего смещения начала развертки, блок задания начального положения развертки и блок смены кадра.

Известные устройства имеют большие габариты и сложную электромеханическую часть интегрирующих приводов вычислительного устройства индикатора истинного движения судовой радиолокационной станции.

Предлагаемое устройство отличается от известных тем, что, с целью устранения указанных недостатков оно содержит блоки логической неравнозначности, блоки запоминания, коммутирующие элементы, блоки слежения и запоминания напряжения, блоки коммутации и инвертирования, причем к соответствующим выходам координатора и к выходам датчиков текущего смещения начала развертки подключены два блока логической неравнозначности, выходы которых через первый и второй коммутирующие элементы подключены к блокам запоминания; управляющие входы первого и второго коммутирующих элементов соединены

C BbIX0ii0ibf блока Cilieilbi кадра; B6IXO+BI 6JIOKOB запоминания подключены к входам соответствующих блоков коммутации и инвертирования, два из которых включены между выходами координатора и входом соответствующего интегрирующего привода, а два других соединены своими входами с соответствующими

10 датчиками текущего смещения начала развертки, а выходами — с входом смещающей катушки индикатора и входом блока смены кадра. Входы блока слежения и запоминания напряжения подключены к выходу соответст15 вующего блока коммутации и инвертирования, к выходу блока задания начального положения развертки и к выходу блока смены кадра, а выход — к входу соответствующего блока коммутации и инвертирования.

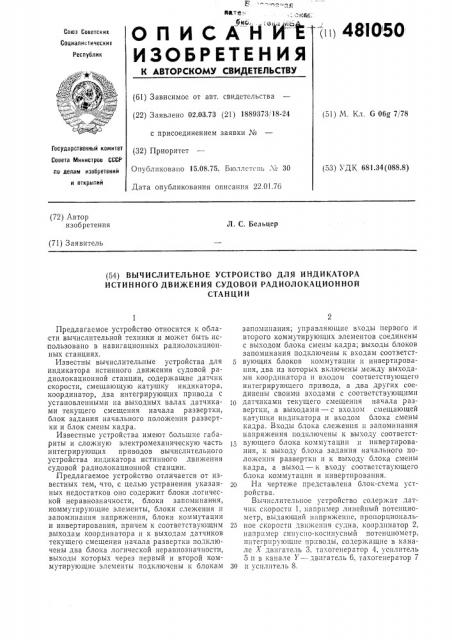

20 На чертеже представлена блок-схема устройства.

Вычислительное устройство содержит датчик скорости 1, например линейный потенциометр, выдающий напряжение, пропорциональ25 Вое скopocTii движения с" дна, координатор 2, например синуспо-косинусный потенцпометр, интегрирующие пр:1воды, содержащие в канале Л двигатель 3. тахогенератор 4, усилитель

5 и в канале У вЂ” двигатель 6, тахогенератор 7

30 и усилитель 8.

481050 с и f>

11япряжснне U,, поступает ня интегрирующий привод канала Х через коммутирующий и инвсртирующий блок, состоящий из опсрациоцпого усилителя 9 и коммутирующего элемента 10. Напряжение U, подастся через коммутирующий элемент 10 пя операционный усилитель 9: в одном случае — ца ипвсртирующий вход И, во втором слу«ac - iia нсинвертирующий вход Н через соответствующие Входные резисторы. На В .Од И пода e i cя тяюкс через резистор напряжение с тахогсцсратора 4.

Напряжение Ь!у поступает ita интегрирующий привод канала Y через коммутирующий и инвертиру!ощий олок, состоящий из операционного усилителя 11 и коммутирующего элемента 12. На операционный усилитель 11 напряжение U, подается черсз коммутирующий элемент 12: в одном случае — на инвсртирую1ций вход И, во втором случае — на цсинвсртирующий вход Н через соответствующие входные резисторы. На вход И подастся также через резистор напряжение с тахогеператора 7.

На выходных валах двигателей 3 и 6 установлены датчики текущего смещения начала развертки 13 и 14, Напряжение с датчнкОВ по ступает на смсщяющую катушку 15 через ком мутирующие и инвертирующие олоки, состоящие из коммутирующего элемента 16 для канала Х (элемента 17 — для ка!)ала Y) и операционного усилителя 18 для капала Х (усилителя 19 — для канала Y) . Напряжение в канале Х поступает на инвертирующий вход И или на неинвертирующий вход H операционного усилителя 18 через соответствующие входные резисторы; напряжение В канале поступает на инвертирующий вход И или на неинвертирующий вход Н операционного усилителя 19 через соответствующие входные резисторы, К выходам координатора 2 и датчика текущего смещения начала развертки 13 (к сигналам а и b) подключен логический блок

20, реализующий функцию логической неравнозначности с сигналом с ня Выхоче блока:

Аналогичный блок 21 подключен к Выходам координатора 2 и датчика текущего смещения цача la развертки 14 (к сигналам d и е) с сигналом g на выходе блока: о d, е.

К выходам 0.70150В 20 H 21 чсрсз комм "«тирующие элементы 22 и 23 подключены блоки

25 и 25 запоминания сигналов неравнозначности. Коммутирующие элементы 22 и 23 по цепям управления подключены к блоку с;!ены кадра 26.

Выходы блоков 25 и 24 подключсны к управляющим входам коммутирующих элемепгов )10, 16 (блок 24), 12 и 17 (блок 25).

К неинвертирующим входам H операционных усилителей 18 и 19 через соответствующие резисторы подключены выходы блоков 27 и

28 слежения и запоминания напряжения. Вхои

)О

)5

2!)

43

4

7Ь1 -)7 И «!!. )ОКОВ Г)0 Ч!С IЮ ICIJI>t К i!ÛÕÎ,)3 0ПCPЯ ционных l cll,)JJTc 7ей 18 l! 1,), t! Iокя 29 33, titilltl-:

11;I чя, )ь)lого;10 )ожс)ц1 5! i! я а. 1«l ря ЗВсртк )1 Ii блока 26 c:5Jc)JI J кадра. Выходы опер !циоиных усилителей 18 1!) Подключены и Bx0;I блока 26.

Предг!яг«7смос Вычисли гс,!! н!)с

P«100T3C1 С, IC:I !0)Ц)!."«1 ООРЯЗОМ.

1 12 П 17 5! Ж C i 11151 с I3 I i .х О;! 0 В I«0 0 p; I i t l 3 TO p 3 2. цроцорццона.7ь):.ыс 1«и 1 )„поступак)т через коммутиру!ощис элсмсн1ы 10:.I 12 и операционные усилители 9;i 11 II«l Вхî !!1 усиг!Птелей

i! 1l 8, и. t! 73 01 «Ipll по чячс н«! Входы Опс p«lционных усил ггслсй 9 ii 11;!апряже:l:ié с r IхогcticpaTopOB 4 и 7, производигс5! JIHTei pltpoВанне вс it!wit!I V, и 1 „в виде поворота валов

Х и Y двиг" òåëåé 3 и 6.

Направление поворота вала двигателя канала Х (или Y) определяется 3Jlаком подаваемой !а шпегрировацис величины U, (или Ь „).

В свою очерс,!ь, этот знак опредс 151cica тем, на какой вход -- И и.lè Н операционного уси,7П7сл51 9 )H чи CH IHTc7 l 11) Ho;Jacl 1121 ряжение U, (или U,,), т. с. положением комм тирующи: элементов 10 (или 12), Состояние жс комму!ирующсг0 элсмсllT2 10 (или элемента 12) определяется запомне:J.tilì в блоке

24 (25) сигналом неравнозначности с (или g) на выходе логического блока 20 (21) Если знак U. (К,) с соответствующего выхода координатора 2 совпадает со знаком сигнала с датчика 13 (14), т. е. если осз операционного усилителя 9111) поворот вала двигателя 2нала Х (У) после смены кадра продолжался бы В ту жс сторону, куда вал двигателя канала Х (У) уже повернут от нулевого полоЖЕНИЯ, ЭТО:5)ОГЛО ОЫ IPHBCC1 И К ТОМ «, ЧТО Ba двигателя канала Х (1 ) дошел бы до упора.

Дл51 уcTpaiILIJH51 такого положения в описанном случае равнозначности сигналов и и A (или d и е), сигнал с=0 (g=O), и на коммутирующий элемент 10 (12) поступает сигнал, при котором напряжение U,. (U„) подастся

112 инвертирующий вход опер яциоп ус! лителя 9 (11), а поворот вала двигателя капала Х (У) после смены кадра обеспечивается

:)с в ту же сторону, куда вал повернут от нуЛСВОГО ПОЛОЖСНИ51, 3 В IIPOTHBOIIOЛОЖНУЮ— к нулевому положению. Но одновременно тот жс сигнал с=0 (g=«0) поступает на коммутирующий элемент 16 (17), и цапря>кение с выходя .1атчика 13 (14) также поступает на инвертирующий вход своего операционного усилителя 18 (191. Благодаря этому, хотя направление поворота вала двигателя канала Х (Y) изменилось на противоположнос, з:)ак изменения величины на выходе операционного усилителя 18 (19) остался тем же, который требовался и был бы без изменения направлеция поворота вала двигателя канала Х i, 1 ) ..

Начальное напряжение после смены кадра

Образуется ila выходе операционного i силитсля 18 (19) при подключении блока 27 (28) и

Выхода блока 29. Блок 27 (28) изменяет )iaпряжснис ня своем Выходе до тех пор, пока

481050 сумма этого напряжения, напряжения с выхода датчика 13 (14) с тем знаком, с которым оно будет поступать в течение начавшегося кадра, и напряжения начального смещения с блока 29 не станет равным нулю. После этого это напряжение запоминается, а блок 29 отключается, и па выходе операционного усилителя 18 (19) остается напряжение начального смещения начала развертки (в дальнейшем оцо будет изменяться с изменением положения валов двигателей 3 и б).

Следует отметить, что запоминание сигналов неравнозначности (с= 1 или с=О; g= 1 или g=0) производится по сигналу смены кадра — только по этому сигналу сигналы с и g поступают из блоков 20 и 21 в блоки 24 и 25 через коммутирующие элементы 22 и 23.

По этому же сигналу смены кадра работают блоки 27 и 28.

После окончания процесса смены кадра в блоках 24 и 25, 27 и 28 запоминаются до новой смены кадра введенные или выработанные в пих величины.

Предмет изобретения

Вычислительное устройство для индикатора истинного движения судовой радиолокационной станции, содержащее датчик скорости, координатор, два интегрирующих привода с установленными на выходных валах датчиками текущего смещения начала развертки, блок задания начального положения развертки, блок смены кадра и смещающую катушку индикатора, о тл и ч а ю ще е с я тем, что, с целью упрощения устройства, оно содержит

5 блоки логической неравнозначностп, блоки запоминания, коммутирующие элементы, блоки слежения и запомппаш1я напряжения, блоки коммутации и инвертирования, причем к соответствующим выходам координатора и к

10 выходам датчиков текущего смещения начала развертки подключены два блока логической неравпозначностп, выходы которых через первый и второй коммутирующие элементы подключены к блокам запоминания; управля15 ющие входы первого и второго коммутирующих элементов соединены с выходом блока смены кадра; выходы блоков запоминания подключены к входам соответствующих блоков коммутации и инвертирования, два из ко20 торых включены между выходами координатора и входом соответствующего интегрирующего привода, а два других соединены своими входами с соответствующим датчиком текущего смещения начала развертки, а выхода25 мп — с входом смещающей катушки индикатора и входом блока смены кадра; входы блока слежения и запоминания напряжения подключены к выходу соответствующего блока коммутации и инвертирования, к выходу бло30 ка задания начального положения развертки и к выходу блока смены кадра, а выход — ко входу соответствующего блока коммутации и инвертирования.

481050 (.оставитедь Л. Ьельцср

Техред T. Миронова

Редактор E. Семанова

Корректор А. Галахова

T«»or»»rt»:и, »р. (:»и 110»а, 2

Заказ 3205/9 Изд. ¹ 1804 ирана 679 Под «ic»oe

Ц1-1ИИПИ Государстве««ого комитета Совета М«»«строк СССР

I10 делам, »!îá»ñ n««é и открыл»и

Москва, )1(-35, Ра шская»аб., д 4,»