Селектор импульсов

Иллюстрации

Показать всеРеферат

1 1

О П И С А Н И Е 48ll28

Союз Советских

Социалистических

Респ;Йик (61) Дополнительное к авт. свид-ву (22) Заявлено 28.08.73 (21) 1955843/26-21 с присоединением заявки № (51) М. Кл. Н 03k 5/18

Совета Министров СССР по делам изабретеиий ч открытий (53) УДК 621.374.33 (088.8) Опубликовано 15.08.75. Бюллетень ¹ 30

Дата опубликования описания 28.10.75 (72) Авторы изобретения

Ю. Г. Голянский и Ю. H. Домченко (71) Заявитель (54) СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ

Госудврствеиимй комитет (23) Приоритет

Изобретение относится к радиотехнике и может быть использовано в автоматической телефонии и вычислительной технике.

Известен селектор импульсов по длительности, содержащий формирователь одиночного импульса, задержанного относительно переднего фронта входного сигнала, две двухвходоыые схемы совпадения и инвертор, причем источник входного сигнала подсоединен к формирователю одиночного импульса и к первому входу одной схемы совпадения непосредственно, а к первому входу другои схемы соыпадения через инвертор.

Однако такои селектор не обеспечивает одинаковой задержки выходного сигнала относительно переднего фронта входного импульса и постоянства длительности выходного сигнала.

Для обеспечения одинаковой задержки ьыходного сигнала относительно переднего фронта входного импульса и постоянства длительности выходного сигнала в предлагаемом селекторе выход формирователя одиночного импульса соединен со вторыми входами схем совпадения.

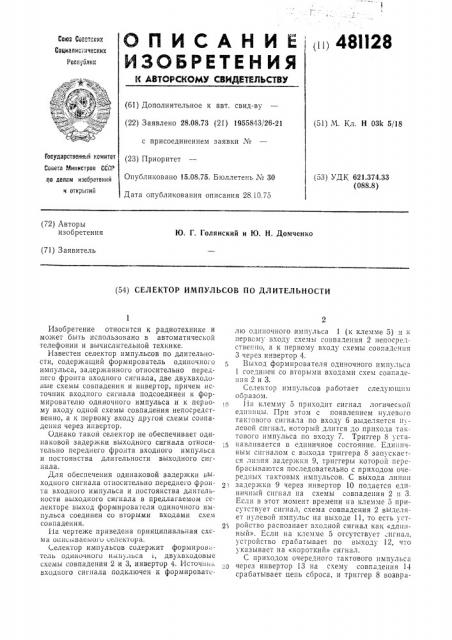

isa чертеже приведена принципиальная схема описываемого селектора.

Селектор импульсов содержит формироы ;тель одиночного и шу,lbcB, двухвходовые схемы совпадения 2 и 3, инвертор 4, Источник входного сигнала подключен к формироватслю одиночного импульса 1 (к клемме 5) и к первому входу схемы совпадения 2 непосредственно, а к первому входу схемы совпадения

3 через инвертор 4.

Выход формирователя одиночного импульса

1 соединен со вторыми входами схем совпадения 2 и 3.

Селектор импульсов работает следующим образом. о Иа клемму 5 приходит сигнал логической единицы. При этом с появлением нулевого тактового сигнала по входу 6 выделяется пулевой сигнал, который длится до прихода тактового импульса по входу 7. Триггер 8 уста15 навливается в единичное состояние. Еди ичным сигналом с выхода триггера 8 запускается линия задержки 9, триггеры которой перебрасываются последовательно с приходом очередных тактовых импульсов. С выхода линии

21 задержки 9 через инвертор 10 подается единичный сигнал на схемы совпадения 2 н 3.

Если в этот момент времени на клемме 5 присутствует сигнал, схема совпадения 2 выделяет нулевой импульс на выходе 11, то есть устройство распознает входной сигнал как «длинный». Если на клемме 5 отсутствует сигнал, устройство срабатывает по выходу 12, что указывает на «короткий» сигнал.

С приходом очередного тактового импульса через инвертор 13 на схему совпадения 14 срабатывает цепь сброса, и триггер 8 возвра481128

Г ) Г 1.L

I ! 1

Состиии;с.",ь Ю. Еркин

Тсхрсд А. Казаикова

h,oððoêToðB!; В. Петрова и О. Данишева

Рсхакто« С. Байкова.«а::аз " 554 20 Ез:!. М 1691 Тирани 902 Подписное

LI,!*1«р!Г!И 1 oc) TI1рствени!1го комитета Совета .в«инистров ССС«-"

I I 0:I c:IcDl из обР стен и!1 H QTI P bi ий

Москва, Ж-35, Рау»иская наб.,;1. 4,.5

Типография, !Ip. Сапунова, 2 щается в пулевое положен! е, и;;и это;i возврагнается в исходное состояние лш»ия задержки 9, а значит и все устройство, и сигнал на выходе пропадает.

Kолпчество триггеров в линии задержки 9 и частота тактовой последовательности выонрается так, что сигнал, формируемый на выходе линии задержки 9, присутствует во времени всегда позже «короткого» входного импульса и до окончания «дли!«!«ого».

Предмет изобретения

Селектор импульсов по длительности, содержащий формирователь одиночного импульс;., задсржа«нного относптслы«о переднего фрон!а входного сигнала, две двухвходовые схем.;! совпадения и инвертор, причем источник входного сигнала подсоединен к формировател!о

5 одиночного импульса и к первому входу одной схемы совпадения непосредстве «но, а к первому входу другой схемы совпадения через и:»вертор, отл и ч а ющи и ся тем, что, с целью обеспечения одинаковой задержки выходного

10 снп«ала от»»осительно переднего фронта входно о импульса и постоянства длительности выходного сигнала, выход формирователя одиночного и., пульса соединен с вторыми входами схем совпадения.