Многопороговый логический элемент

Иллюстрации

Показать всеРеферат

1 1 фЛ! >1 би(11, н . ° -.:, .. ° — ° E

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДН ЕДЬСТВУ (1 481136

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 04.10.72 (21) 1835433/26-21 с присоединением заявки— (23) Приоритет—

Опубликовано 15.08.75. Бюллетень;¹ 30.

Дата опубликования описания 19.01.76 (51) М. Кл. Н 03k 19/42

Н ОЗ! 5/20

Государственный комитет

Совета Министров СССР

Ilo делам изобретений и аткро(тий (088.8) (72) Автор изобретения

В. Л. Дшхунян (71) Заявитель (54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к логическим устройствам, применяемым в вычислительной технике и автоматике, в частности к многопороговым логическим дискриминаторам для многопороговых логических элементов.

Известен многопороговый логический элемент, содержащий линейный сумматор с парафазным выходом и многопороговый дискриминатор.

Для повышения быстродействия в предлагаемом элементе многопороговьш дискриминатор состоит из переключателей тока на пяти транзисторах, включенных по схеме с оощим коллектором, и схемы совпадения на многоэмиттерном транзисторе, к одному из эмиттеров которого подсоединен эмиттер третьего транзистора переключателя тока, а к остальным его эмиттерам подсоединены попарно соединенные эмиттеры первого и пятого, второго и четвертого транзисторов переключателей тока, причем базы первого и второго транзисторов подсоединены к прямому выходу вышеупомянутого линейного сумматора, состоящего из четырех входных транзисторов, эмиттеры которых соединены соответственно с эмиттерами четырех — эмиттерного транзистора с резистивными делителем напряжения в качестве его коллекторной нагрузки, средние выводы которого соединены соответственно с базами третьего, четвертого

1I пятого транзисторов многопорогового дискриминатора, коллектор многоэмпттсрного транзистора которого соединен с базой выходного эмиттерного повторителя.

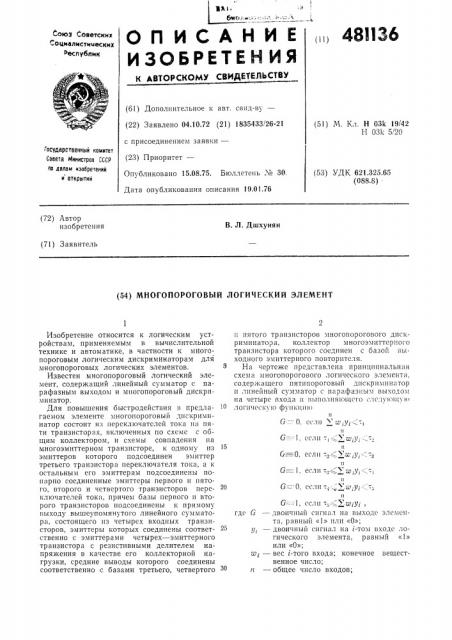

На чертеже представлена принципиальная схема многопорогового логического элемента, содержащего пятипороговый дискриминатор

tt линейный сумматор с парафазным выходом на четыре входа и выполняющего слс;1ую1цуi(> логическую функ(IIIII>

11

6 О. если " г,y(i -i

l1

6 — 1, сслп -.,- «ы,у, - « !

6==0, сслп —.зУо:(,у,-. -., 11

G==-.. 1, если .1 ° юД ; . и

6=-. О, сс.п! .,- .- . и .y;-11

G=: — 1, сслп -.-,-.)ы;у;, где G — двоичньш сигнал на выходе элемента, равньш «1» плп «О»; (/, — двоичный сигн11л на /-том входе to" гического элемента, равньш «1» или «О»;

w — вес 1-того входа; конечное вещественное число; и — общее число входов;

481I36

-.„ „" „-.,„-.,- — соответствующие пороги многопорогового логического элемента, конечные вещественные числа.

Многопороговый логический элемент состоит из линейного сумматора, выполненного на четырех входных транзисторах 1 — 4, опорном четырех эмиттерном транзисторе 5, «весовых» резисторах 6 — 9, источниках напряжения 10 и

11, и многопорогового дискриминатора, выполненного на переключателях тока на пяти транзисторах 12 — 16, включенных по схеме с общим коллектором, и резисторах 17 — 24, схеме совпадения на многоэмиттерном транзисторе 25 и резисторе 26, выходного эмиттерного повторителя на транзисторе 27, резисторе

28, и источника напряжения 29, Многопороговый логический элемент работает следующим образом.

В исходном состоянии транзисторы 1, 2, 3, 4, 14, 15, 16 выключены, а транзисторы 12 и

13 и многоэмиттерные транзисторы 5 и 25 включены, На выходе элемента — уровень логического нуля.

Рассмотрим для примера работу пятипорогового логического элемента с «весами входов (1, 1, 2, 2)» и «порогами 1, 3, 4, 5, 6».

Относительный «вес входа 2» означает, что сопротивление соответствующего резистора в два раза меньше сопротивления резистора на входе с «весом 1».

У выходного транзистора 25 схемы совпадения проводит только эмиттер, связанный с эмиттером транзистора 14, срабатывающего на минимальный «порог 2», Входные двоичные сигналы, поступая на базы входных транзисторов 1, 2, 3, 4 изменяют потенциалы на базах транзисторов 12, 13, 14, 15, 16 в многопороговом дискриминаторе. Если «весовая»

>1 Л сумма включенных входов,, ы;у;, 1 < )ы,у, <3, то транзистор 14 включается. выключая транзистор 25 схемы совпадения и устанавливая иа выходе элемента логическук> единицу и

Если 3- = ) z,ó,<4, то транзистор!4 включается, l транзистор 13 выкл>очнется н на выходе --- уровень логического нуля. и

Если 4 4 сс>,.у; <5, то транзистор 14 включается, транзистор 13 выключается, ио включается транзистор 15 н иа выходе— уровень логической единицы.

11

Если 5.<"."сс>,.у,<6, то транзисторы 14 и

15 включая>тся, транзистор 12 и 13 выключаются, IIa выходе — логический «О».

t7

Если ; сс>,. у, = 6, то транзисторы 14, 15, 16 включаются, транзисторы 12 и 13 выключаются, транзистор 25 схемы совпадения выключен и на выходе — логическая единица.

Таким образом элемент выполняет пятипороговую логическую функцию. Использование мно гонор оговых логических элементов при построении логических устройств позволяет в

>и несколько раз повысить быстродействие всего логического устройства и сократить оборудование по сравнению с аналогичными логическими устройствами иа однопороговых логических элементах.

>5 Схем» содержит компоненты, легко реализуемые монолитной интегральной технологией и не требует жестких допусков к напряжению питания и параметрам компонентов. В интегральных схемах заданные отношения ре20 зисторов можно легко выдержать с точностью +2О>>о и даже лучшей, при таких допусках нетрудно получить четырех и пятипороговые логические элементы. Схема обладает наибольшим быстродействием по сравне25 нию с известными в виду возможности работы транзисторов в ненасыщенном режиме.

Предмет изобретения

">1ногопороговый логический элемент, содержащий линейный сумматор с парафазным выходом и многопороговый дискриминатор, отличаюишйся тем, что, с целью повышения быстродействия, многопороговый дискриминатор состоит из перек:почателей тока на пяти транзисторах, включенных по схеме с общим коллектором, и схемы совпадения на многоэмиттерном транзисторе, к одному из эмиттеров которого подсоединен эмиттер третьего транзистора переключателя тока, а к остальным его эмиттерам подсоединены попарно соединенные эмнттеры первого и пятого, второго и четвертого транзисторов переключателей тока, причем базы первого и I>Topolo транзи 5 сторов подсоединены к прямому ьыходу вышеупомянутого линейного сумматора, состоящего из четырех I>xoIIIII»x транзисторов, эмиттсры которых соединены соотвстственно с эмиттерами четырехэмиттсрного транзистора с резистивиым делителем напря>кения в качестве его коллекторной нагрузки, средние выводы которого соединены соответственно с базами третьего. четвертого и пятого транзисторов многопорогoI>olo дискриминатора, коля>> лектор миогоэмиттсрного транзистора которого соединен с базой вь>ходного эмиттерного повторителя.

Г !

Вход

I ! !

Составитель В. Назарова

Редактор С. Байкова Техред Л. Казачкова Корректор Т. Миронова

Заказ 7938 Изд. № 1736 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Череповецкая городская типография