Устройство для проверки схем сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

О П И С А Н И Е (и) 48I888

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено16.07.73 (21)1942926/I 8-24 (51) М Кл (О(; I 1уiiО с присоединением заявки №

Гооудерстеенный комитет

Совете Министров СССР во делам изобретений и открытий (23) Приоритет (43) Опубликовано25.08.75 Бюллетень ¹3l (53) УДК6Ь l.332. .65 (088.8) (45) Дата опубликования описания 18.11.7

О. Il. Мацкевич (72) Автор изобретения (71) Заявитель (54) УСТРОЙС 1 ВО ДЛЯ ПРОВЕРКИ СХЕМ

СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к автоматике и вычислительной технике и может быть использоваио при реализации технических средств проверки электронных блоков дискретной автоматики н вычислительных машин.

l1: веси о устройство для проверки схем сравнения двоичных чисел, содержашее триггеры, логический блок, два счетчика, входы которых через соответствуюшие схел1ы "И" соединены с шиной тактовых сигналов, а Ip выходы подключены к входам проверяемой схемы ср«инеыия.

Однако в указаннол устройстве не предусмотрено «втоматическое изменение сдвига между числал и в счетчиках, необходимое I5 для полной проверки схемы сравнения, в результате чего усложняется проверка схемы сравнения.

Бель изобретения - упрошение работы устройства. Достигается это тем, что в уст-20 ройстве прямой и инверсный выходы первого триггера соединены с другими входами схем "И соответственно, выходы последних разрядов счетчиков соединены с входами установки в единичное и нулевое состояние 25 этого триггера соответственно; счетный вход первого триггера соединен с инверсным выходом второго триггера, счетный вход которого подключен к шине тактовых сигналов, прямые выходы триггеров и выход проверяемой схемы сравнения подключены к входам логического блока.

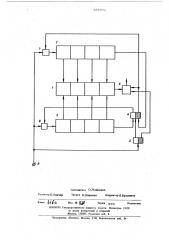

На чертеже приведена блок-схел а устройства.

Устройство содержит проверяемую схему сравнения I., счетчики 2 и 3, триггеры 4 и 5, логический блок 6, схемы "И" 7 и 8.

Входы счетчиков 2 и 3 соединены через схемы "И 7 и 8 соответственно с шиной тактовых сигналов 9. Вторые входы схем

"И" 7 и 8 соединены соответственно с нрямым и инверсным выходом триггера 5, входы установки в единичное и нулевое состояние которого соединены с выходами счетчиков 2 и 3 соответственно. Счетный вход триггера 4 соединен с прямым выходом триггера 5, счетный вход которого соединен с шиной тактовых сигналов 9. Выходы схемы сравнения 1, триггеров 4 и 5 лод481898

0 1 0 0

1 0 1 0

0 1 0

1 0 0 1

1

45

3 ключены к логическому блоку 6, выход которого является выходной шиной устройства.

Устройство работает следующим образом.

Перед началом проверки счетчики 2 и .3 и триггеры 4 и 5 устанавливаются в нулевое положение сигналом "сброс" (цепи сброса на схеме не показаны). При этом схема

И 8. открыта, а схема сравнения выдает на логический блок 6 сигнал Х1 (А-В, где А и В - числа в счетчиках 2 и 3 со- 10 ответственно). Логический блок 6 сравнивает сигнал Х1 с состоянием триггеров 4 и 5 (состояние 00" — оба триггера в нулевом состоянии). Логический блок 6 выдает сигнал "исправно " при наличии сигнала Х1 или сигнал "неисправно" при отсутствии сигнала Х1.

Первый тактовый импульс записывает единицу в счетчик 3 (A=O, B=1) и опрокидывает триггеры 4 и 5 (состояние 11").>0

При этом триггер 4 закрывает схему "И"

8 и открывает схему ":! 7, а схема сравнения 1 должна выдавать сигнал Х2 (ACB), Второй тактовый импульс записывает единицу в счетчик 3 (А=1, В=:1) и устанавливает триггер 5 на ноль (состояние

"10"). При этом схема сравнения 1 должна выдать сигнал Х1 (А=В).

Третий тактовый импульс проходит также на счетчик 2 (А=2, В=1) и опрокиды,вает триггеры 4 и 5 (состояние 01). При этом триггер 4 закрывает схему И" 7 и открывает схему "И" 8, а схема сравнения 1 должна выдавать сигнал Х3 (А>В)..

Четвертый тактовый импульс записывает

I единицу в счетчик 3 (А=2, В=2) и устанавливает триггеры 4 и 5 в исходное состояние 00.

На этом заканчивается полная проверка младшего разряда схемы сравнения 1.

Проверка последующих разрядов производится аналогично,эа исключением последнего разряда. На предпоследнем такте проверки последнего разряда счетчик 2 переполняется (А=О, В> О) и схема сравнения должна выдать сигнал Х2. Для правильной работы логического блока 6 триггеры 4 и 5 переводятся из состояния "01" в состояние "11" импульсом переполнения счетчика 2, который подается на единич50

4 ный вход триггера 4 (при необходимости вводится небольшая задержка). На послед(" нем такте йроверки последнего разряда переполняется счетчик 3 (АЖ, В=О), при этом триггеры 4 и 5 перейдут в состояние

10. Для правильной работы устройства при повторной проверке схемы сравнения триггеры 4 и 5 переводятся в состояние

00 импульсом переполнения счетчика 3, который подается на нулевой вход триггера 4.

Логическое устройство 6 строится в соответствии со следующей таблицей состояний.

Тг4 Тг5 Х1 Х2 ХЗ

Выход Х1 схемы сравнения 1 может быть обьединен с выходом Х2 или Х3.

Предмет изобретения

Устройство для проверки схем сравнения двоичных чисел, содержащее триггеры, логический блок, два счетчика, входы которых через соответствующие схемы И" соединены с шиной тактовых сигналов, а выходы подключены к входам проверяемой схемы сравнения, о т л и ч а ю щ е ес я тем, что, с целью упрощения работы устройства, в нем прямой и инверсный выходы первого триггера соединены с другими входами схем "И соответственно, выходы последних разрядов счетчиков соединены с входами установки в единичное и нулевое состояние этого триггера соответственно, счетный вход первого триггера соединен с инверсным выходом второго триггера, счетный вход которого подключен к шине тактовых сигналов, прямые выходы триггеров и выход проверяемой схемы сравнения подключены к входам логического блока.

Редактор Е.Гончар

Заказ Я/ .

Изд. М Яф Тираж @79

Подписное

Составитель О.Малькевич

Техред H.Xaaeeaa Корректор Л.Брахннна

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб. ° 24