Устройство для вычисления площадей пиков хроматограмм

Иллюстрации

Показать всеРеферат

Своз Советских

Соцммистимеских еесп облик

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

Н АВТОРСИОМУ СВИДЕТЕЛЬСТВУ (t)) 481917 (61) Дополнительное к авт. свид-ву (22) Заявлено 02.06.7(21) 1792437/ 18-24 (50.М. Кл. (06 37/00

C 01 7/32 с присоединением заявки № (23) Приоритет(43) Опубликовано 25.08.7ЦБюллетень № 31

Гааударставннаа намнтат аванта Мнннетраа СССР нв делам нзваратвннй н открытий (бЗ) УДК

681. 332;5 1 (088. H ) (45) Дата опубликования описания 11.11.75 (72) Авторы изобретения

Б. Г. Кадук, А. А Кравченко и С. И. Рудковский (71) Заявитель Всесоюзный научно-исследовательский институт аналитическрго приборостроения (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПЛОЩАДЕЙ ПИКОВ

ХРОМАТОГРАММ

Изобретение относится к вычислительной технике и может нафти применение при исследовании спектральных .характеристик, например при вычислении площадей пиков .хроматограмм. 5

Известны интегрирующие устройства, вычисляющий площади пиков хроматограмм путем преобразования аналоговых величин амплитуд сигнала в частоту следования импульсов и суммирования их в течение време-пт ,ни развертки;

Однако эти устройства .характеризуются низкими быстродействием и точностью, малым динамическим диапазоном измеряемых параметров сигналов, сложностью. И

Цель изобретения — повышение быстродействия и точности вычисления площацей пиков .хроматограмм.

Для ее осуществления предлагается . устройство, которое содержит блок порого- СО вых элементов, дифференциальный усилитель и аналого-цифровой следящий преобразователь, аналоговый вход и выход которого соединены с соответствующими входами дифференциального усилителя, два цифровых 26 входа подключеиы соответственно к выходу генератора импульсов и к выхоцу блока схем совпадения, а цифровой выход присо, единен к информационному входу регистра сдвига, выход дифференциального усилителя поцключен к входу блока пороговых элементов, выход которого соецннен с вторым входом блока схем совпадения и с управляющим входом регистра сдвига.

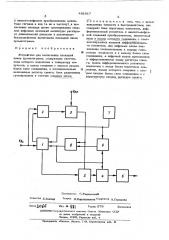

На чертеже приведена блок-схема уст; ройства.

Аналоговый вход аналого-цифрового сле: дящего преобразователя 1 и один из вхо, дов дифференциального усилителя 2 соединены с входом устройства. Второй вход дифференциального усилителя соединен с аналоговым выходом преобразователя 1.

Цифровой выход преобразователя 1 соединен через информационный вход регистра сдвига 3 и блок разрешения суммирования

4 с входом счетчика кодовых чисел 5.

Один. цифровой вход преобразователя 1 и ,вход счетчика 6 соединены с выходом генератора импульсов 7, а второй цифровой вход преобразователя 1 соединен с одним

481917 б

35

45 выходом блока схем совпадения 8, со г вторым входом блока разрешения суммирования 4 и с входом ".сброс счетчика 6.

Выхоц дифференциального усилителя 2 соединен с входом блока пороговых элементов В,выход которого соединен с вторым входом блока схем совпадения 8 и с управляющим вхоцом регистра сдвига 3, Аналого-цифровой следящий преобразователь 1 прецназначен для цифрового преобразования текущих значений амплитуды входного сигнала, выдачи результатов че1 рез регистр сдвига 3 и блок разрешения суммирования 4 в счетчик кодовых чисел

5, а также для формирования совместно с дифференциальным усилителем 2 на вход блока пороговых элементов 9 разностного сигнала Vz>- V<, где V, — входной сигнал, Y — компенсирующий сигнал с аналого,вого выхода преобразователя. Блок порого,вых элементов включает в себя ft пороговых элементов, настроенных на пороги срабатывания, соответствующие кодовым чисо лам 2, 2,..., 2, и схему выделения сигнала одного из сработавших элементов, порог срабатывания у которого наибольший.

С выхоцов 2, 2, ..., 2 пороговых элементов производится управление в сдвигающем регистре 3 величиной сдвига влево на 1, 2, 3 ..., П, разрядов считываемого кода текущих значений входного сигнала, т. е. деление ко1да входного сигнала соответственно в 2, 2, ..., 2 раза, а

2 также управление через блок схем совпадения 8 и блок разрешения суммирования

4 частотой суммирования результатов цифрового преобразования в счетчике кодовых чисел 5. Управление скоростью (а также и цискретностью) преобразования амплитуды входного сигнала в код осуществляется сигналами с выходов блока схем совпацения 8, поступаемыми ра цифровые о (счетные) входы 2, 2, ... 2 аналого-цифрового следящего преобразователя 1, для чего каждый из выходов 2 и

2, ... 2 пороговых элементов и соответственно кажцый из выходов 2,2,,2 счетчика 6 соединены попарно через одну из двухвходовых схем совпадения блока схем совпацения 8 с одним из счетных входов преобразователя 1, т. е. со счет, о ным входом 2 преобразователя 1 соецинены через схему совпадения выход 2 о блока пороговых элементов 9 и выход

21 счетчика 6, со счетным входом

2 преобразователя 1 через схему совпацения соединены выход 2 блока пороговых элементов 9 и выход 2 1 счетчика 6 и т. ц.

Устройство работает следующим образом.

В момент, предшествующий началу вычисления, а также после включения устройства при величине амплитуды входного сигнала меньшей значения наименьшего из порогов срабатывания блока пороговых элементов 9, аналого-цифровой следящий преобразоваи ель 1 находится в Ъулевом" состоянии и разностный сигнал с выхода дифференциального усилителя 2 отсутствует, а следовательно, отсутствуют и управляющие сигналы с выходов блока пороговых элементов 9. В этом случае отсутствуют сигнаI лы и с выходов блока схем совпадения 8, ччто препятствует прохождению счетных импульсов с генератора импульсов 7 в аналого-цифровой следящий преобразователь 1, поддерживая его в "нулевом" состоянии. По мере нарастания амплитуды входного сигнала до величины срабатывания пороговых элементов блока 9, последние срабатывают, а схема выделения сигнала одного из них, порог срабатывания у которого наибольший, определит через регистр сдвига 3 коэффициент,целения считываемого кода амплитуды; через соответствующие выход блока пороговых элементов 9 и одну из двухвхоцовых схем

I совпадения блока 8 определит дискретность и скорость цифрового преобразования амплитуды вхоцного сигнала, а также частоту установки в "О" счетчика 6, заполнение которого производится в интервалы между срабатываниями одной из схем совпадения блока 8 и через блок разрешения суммирования 4 частоту суммирования текущих цифровых значений амп литуды счетчиком кодовых чисел 5. При выбранной определенной постоянной частоте следования импульсов, заполняющих счетчик 6, частота появления управляющих сигналов с выхода блока схем совпадения

8, т. е. скорость аналого-цифрового пре образования амплитуды входного сигна ла, а также выбор величины шага дискретности аналого-цифрового преобразования осуществляются в прямой зависимости от скорости нарастания амплитуды входного (сигнала.

Такий образом, устройство автоматически изменяет шаг квантования амплитуцы входного сигнала (пика) по времени, что позволяет снизить погрешность аппроксимации при вычислении плошадей,хроматограмм с заметно отличающимися крутизной фронтов, ю

481917

Соста антея ь С. Радковский

ТекРед И.1 арандашова КоРРектоР Д.. aaaxoaa

Редактор Е.Гончар

Заказ О р изд м 93t Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24 а аналого-цифровое преобразование амплитуды сигнала в код (а не в частоту),.и вычисление площади путем суммирования текущих цифровых значен;ий амплитуды расширяет динамический диапазон и увеличивает быстродействие вычисления площадей пиков .хроматограмм.

Предмет изобретения 10

Устройство для вычисления площацей пиков хроматограмм, соцержащее счетчик, вход которого подключен к генератору импульсов, а выход соединен с первым вхоцом блока схем совпадения, и последовательно 15 ,включенные регистр сдвига, блок разрешения суммирования и счетчик кодовых чисел, о т л и ч а ю щ е е с я тем, что, с целью: повышения точности и быстродействия, оно содержит блок пороговых элементов, дифференциальный усилитель и аналого-цифровой следящий преобразователь, аналоговый вход и выход которого соецинены с соответствующими вхоцами дифференциального усилителя, два цифровых входа поцключены соответственно к выходу генератора импульсов и к выходу блока схем совпадения, а цифровой выход присоединен к информационному входу регистра сдвига, выход дифференпиального усилителя подключен к входу блока пороговых эле-! ментов, выход которого соецинен с вторым входом блока схем совпадения и с управляющим входом регистра сдвига.