Следящий преобразователь функций вида у=

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистимеских

Республик (1 ) ) 431918

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 25.12.72(21) 1862618ó1824

{5}) М. Кл.

С- 06 3/00

3 с присоединением заявки №

Гасударственный «амнтет

Савета Иннистрав СССР аа делам изобретений н аткрытнй (23) Приоритет (53) УДК

681.34(088.8) (43) Опубликовано 25 08 75 Бюллетень №З1 (45) Дата опубликования описания 11.11.75

Б. Г, Кадук, С. И. Рудковский, Г. А. Зборовский и Нгуенг Ба Шау (?2) Авторы изобретения

Всесоюзный научно-исследовательский институт аналитического приборостроения (54} СЛЕДЯЩИЙ ПРЕОБРАЗОВАТЕЛЬ ФУНКЦИЙ ВИДА

У= N

Изобретение относится к вычислительной технике и может быть использовано в устройствах коррекции погрешностей и

1 цругих специализированных устройствах для непрерывного вычисления показательх ных функций $ = N, где се u x — переменные, зацаваемые соответственно в цифровой и аналоговой формах.

Известно, что вычисление показательных функций на ЭЦВМ сложно и не обла- щ ,цает быстродействием.

Цель изобретения — повышение быстродействия вычисления показательных функций с выдачей результата в цифровой форме и упрощение преобразователя. 15

Достигается это путем преобразования ,двоичного числа Я в одном логарифмато ре в аналоговую величину /а тИ»умножение двух аналоговых величин К to) N1 и изменение на вхоце второго логарифматора кода числа И„ с оцновременным преобразованием его Ъ величину 4 N qo момента равенства выходных аналоговых сигналов Х ярдg й, = Год N, т. е. цля чего преобразователь соцержит пва I логарифматора, .цва реверсивных счетчика,, множительный блок, сравнительный блок и схему совпадения.

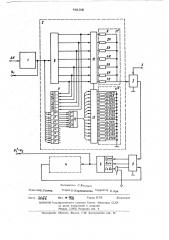

На чертеже привецена блок-схема преобразователя.

Вход реверсивного счетчика 1, осуществляк>щего суммирование или вычитание импульсов в зависимости от знака вводимой переменной величины, соединен с входом преобразователя, через который вводится переменная величина — Ь Й, прецставляющая собой последовательность счетных импульсов. Выхоц реверсивного счетчика 1 соединен с входом яогарифматора

2 и с выходом преобразователя hl контролирующим суммарное показание

1 счетчика в течение всего времени преобразования. Выход логарифматора 2 соединен с входом множительного блока 3, второй вхоц которого соединен с вторым входом .х преобразователя, через который вводится значение переменной x — пока.х зателя функции у = Я и предназначенное для выполнения операцииХ "а >81 B " xоцы множительного блока 3 и второ и ло .

481918

30 гарифматора 4 соединены с входами блока сравнения 5, три выхода которого соединены с входами второго реверсивного счетчика 6 суммирование, вычитание" и через схему совпадения 7 со счетным 5 входом. Блок сравнения прецназначен для вклкчений реверсивного счетчика 6 в режимы: суммирования при g fo < N< > (a >tq> вычитания IIpH )(f g }4 (я останова при К (@у

Выход реверсивного счетчика 6 соединен с выходом преобразователя л(, с

1 которого считывается результат вычислений при xi p =

;одкп1очения одного из сопротивлений 8, . 2Й, ... 7Я, резисторной матриуы 111 к части резисторной матрицы 11 дробных значений O>105$; О, 185/; 0,265Ь „О,325R;

0,385 ; 0,465M; 0,525/; 0,570 ; 35

0,650Я; 0,7101"„0,760Р„0,815К;

0,875ф 0,910Р, 0,970$, Выходы блока.

8 выцепения старшего значащего разряда соединсиы также с уйравпяющими .входами сдвlrl-aIGII,его регистра 9 таким образом, что при коде числа Я со старшим зиа21 члщим разряцом 2,2 ипи 2 производится сцвиг кода числа N на 3,2 или 1 раз1 ряц вправо (умножение) соответственно, 4> а дпя числа Я со старши. м значащим разряцом 2, 2 или 2 - на 1, или

3 разряда влево (ууленде) соответственно. о

>>II:оцы 2, 2, 2, 2 сдвига1о цего, рег утра 9 соединены с входами 2, 2, 2, 5р

2 дешифратора 12, а выходы последнего с управляющими входами коммутатора 13, ключи которого стоят в цепях сопротивпе2 ний дробной части матрицы 11 . Один коммутирующий выход каждого ключа соединен с соответствующим сопротивлением, а вторые выходы ключей целой и дробной матриц, соецинены между собой. Общая точка схемы, объецинянщая вторые выводы сопротивлений кратных („ является выхо- 6О дом погарифматора 2,4, а оби.аи точка, объединяюшая вторые выводы сопротивлений меньших Ц, соединена с корпусом.

Алгоритм вычисления логарифмов чисел заключается в следующем.

Показатель степени старшего значащего разряда двоичного числа М численно равен характеристике 4Щ Й .

Располагая значениями мантисс логак .к+1 рифмов всех чисеп . в интервале 2 - 2 (в данном логарифматоре используются предварительно вычисленные с определенной точностцо зн аления мантисс чисел B интервале 2 — 2, К = 4) достаточно дпя вычисления с помощью логарифматора с той же к точностью всех чисел, меньших 2 (дпя данного логарифматора меньших 2 ), 3

Таким образом,,цля вычисления мантисс логарифмов чисел меньших 2, необходимо 4» PI умножать эти числа на 2 (где Щ старший значащий разряд числа g ), после чего значение мантиссы IIIIGIII полученного числа берется из известц го ассива логарифмов чисел в интервале 2 -, 2, что

) аналогично - сдвигу кода числа М вправо на

1ТЪ разрядов.

Аналогично для вычислени мантисс по, к гарифмов чисел М >2 (Я) 2 ) необходилт-К, щ- мо умножить эти числа на 2 (2 ), после чего значение мантиссы вновь полученного числа берется из известного массик к+1 ва логарифмов чисел в интервале 2 2 (2 2 ), что аналогично сдвигу кода числа М влево на М разрядов.

Исходная информация в логарифматоре представлена в виде номиналов conpoòèâIIåIIIIf К, 28, ... 7Я (для вычисления .характеристики) и номиналов сопротивлений Я (1, численные значсция которых соответствуют мантиссам логарифмов чисел в интервале

«Э

2 — 2 . Выбор необхоцимого значения .характеристики логарифма двоичного числа

Я производится через коммутатор 10, управляемый блоком 8 выделения старшего значащего разряда, а выбор значения мантиссы осуществляется через коммутатор 13, управляемый с выходов дешифратора 12, количество выходов которого равно количеству номиналов,цробных значений Р.

Преобразователь работает следующим образом.

Предположим на входах преобразователя (входы реверсивного счетчика 1 и г,lnoжитепьного устройства 3) присутствуют переменные величины Aha, .х и в реверсивном счетчике 1 сфоомировано число К, 1апример, (1 —, 02 + 12 + 12,,+,02 +

3 2 1: Ь

+ 0 2 + 12 + 12 + 12 =- 103 введенное в погарифматоре 2 в блок

481918

8 вьщепения старшего значащего разряца и сдвигающий регистр 9. Блок выделения старшего значащего разрра выделит из кода чисел Я разряд 2, в результате

1 чего на соответствующем его выходе поя-, вится управляющий сигнал, с помощью которого через коммутатор 10 к коммутатору 13 будет подключено сопротивление

6g. Одновременно этим же сигналом будет произведен сдвиг кода числа Й в 10 регистре 9 на 1И вЂ” К (т.е. 6 - 4 = 2) разряда влевц и с выхода дешифратора 12 через комммутатор 13 последовательно к сопротивлению 6 будет поцключено сопротивление 0,650R. 15

Суммарное сопротивление 6,650+ или эквивалентные ему величины тока или напряжения в множительном устройстве 3 на аналоговую величину х и результат Х 4)gN, поцается на один вход устройства сравне- 20. ния 5, на второй заход которого с выхода логарифматора 4 поступает сигнал, пропорциональный 4 N > l rye Х вЂ” значейие вы-

2 .ходного кода реверсивного счетчика 6. При

Xtq N ) Log N Z с выхода устройства срав-25 пения на реверсивный счетчик 6 поступает сигнал, переключающий счетчик в режим суммирования. В этом случае происхоцит заполнение реверсивного счетчика 6 импульсами через схему сопротивления 7 и З0 преобразование получаемого числа в логарифматоре 4 в его логарифм цо тех rtop, пока не наступит равенство Х О9 Й = г

013 М g, что означает М = Я и схе-! ма совпацения 7 закрывается, прейятствуя поступлению счетных импульсов. Аналогичная операция производится при ХЬ Я С 4> N

21„ 22 с той лишь разницей, что реверсивный счетчик 6 работает в режиме вычитания.

Преобразователь обладает высоким 40 быстроцействием, ограниченным в основном временем срабатывания ключей коммутаторов.

Преобразователь может. быть использован просто цля вычисления доказательных 45 функций, цля чего значение функция в цвоичном коде ввоцится непосрецственно в»огарифматоре 2

Предмет изобретения

1. Следящий преобразователь функций х вида у = N содержащий цва реверсивных счетчика, блок сравнения и схему совпадения, о т л и ч а ю ш и и Ч я тем, что, с целью повышения быстроцейст- вия и расширения функциональных возможностей, в него введены цва погарифматора и множительный блок, причем первый вход преобразователя через последовательно соединенные первые реверсивный счетчик и логарифматор поцключен к первому входу множительного блока, цругой вход которого соединен с вторым входом преобразователя, а выход подключен к первому входу блока сравнения, соециненного вторым входом с выходом второго логарифматора, рход которого соединен с выходом второго реверсивного счетчика, причем входы управления реверсом последнего подключены к выходам блока сравнения, а счетный вход — к выходу схемы совпадения, подключенной входами к вы.ходу блока сравнения и шине счетных импу»ьсов.

2, Преобразователь по и. 1, о т » и — ч а ю шийся тем, что каждый логарифматор соцержит два коммутатора, цве резисторные матрицы, дешифратор, регистр сдвига и блок выделения старшего значащего разряда, соединенный входом с вхоцол логарифматора и информационным входом регистра сдвига, а выходом поцключенный к управляющим входам первого коммутатора и .управляющим входам регистра сдвига, выход которого через дешифратор подключен к управляющим вхоцам второго коммутатора, причем одни коммутирующие вы.хоцы каждого из коммутаторов соединены с входами соответствующей резисторной матрицы, а вторые выходы соецинены межцу сорой,, РедактоРЕ ГончаР

Техред К,1 арандашова Корректор 11 А ук

Изд М 9Ь

Заказ gggg

Тираж 679

Подписное

Г1редприятие «Патент», Москва, Г-59, Бережковская наб., 24

ЦИИИ11И Государственного комитета Совета Минн«тров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4