Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскии

Социалистических республик (<>) 481938 (61) Дополнительное к авт. свид-ву (22) Заявлено 14.09.73 (21) 1958964/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 25.08.75 Бюллетень № 31

Дата опубликования описания 2З.1О.7 (51) М. Кл. (11с 11/08

Гооударотвенный комитет

Совета Министроа СССР по делам изобретений н открипий (53) УДК 681.327.66 (088. 8) (72) Авторы изобретения

E. П. Балашов, Е. E. Владимиров, В, Г. Корчагин и Л. N. Хохлов

Ленинградский ордена Ленина электротехнический институт (71) Заявители нм. В.И.Ульянова (Ленина) и Государственное союзное конструкторско— технологическое бюро по проектированию счетных машин (54) ЗАПОМИНАЮ1ЦЕЕ УСТРОИСТВО

Изобретение о носится к вычислитель: ной технике, в частности, к запоминающим устройствам.

Известно запоминающее ус гройство (ЗУ ), содержащее накопитель на числовых ферритовых линейках с отверстиями записи и опроса, прошитыми соответственно шинами считывания, разрядного тока запрета и опроса,причем каждая шина опроса прошиra через отверстия опроса в прямом направлении

,по каждому адресу в отдельности, формиро ватели адресных и разрядных токов и усилители считывания, подключенные к соответствующим обмоткам, и селектирующие диоды.

Цель изобретения — расширение функциональных возможностей устройства.

Для осуществления устройство содержит формирователи младшего разряда адреса, I формирователи первого и второго операндов, подключенные соответственно к началам шин первого и второго операндов; каждая шина опроса прошита дополнительно через отвер- стия записи в обратном направпении но каждому адресу в отдельности; начала шин

- опроса через селектируютцие диоды соеди1нены. с соответствующими форл проватепями младшего разряда адреса, а концы шин опроса подключены к формирователю старшего разряда адреса, шины петвого и второго ( операндов прошиты с ответственно через отверстия записи и отверстия опроса всех числовых ферритовых линеек по каждому адресу в отдельности, причем концы этих ттт шин через селектирующне диоды соединены с соответствующими формнроватепями литад- шего разряда адреса.

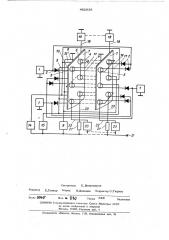

> На чертеже изображено запоминающее, устройство емкостью три Я -разрядных

)5 слова. формирователи 1 младшего разряда ад реса через селектирукщие диоды 2 соединены с началами шин 3 опроса. Шины 4 опроса пропущены через огверстия 5 онро-

Qfj са и встречно через отверстия 6 записи двухотверстных числовых феррнтовых линеек 7, нри этом концы шин 8 опроса объединены и группу и присоединещ,! к формирователю 9 старшего разряда алвеса. Ша»ы 30

З5 первого операнда»рошнты ч,.ре; он верон i|я.I

481938 Ьыполняемая функция

М икротакт х запр.

0 0

1.

Конъюнкция

2=X У

1 0

0 0

Дизъюнкпия

7„= хУ7

1 0

0 0

1 0

0 1

1 1

Равнозначность двух высказываний

Z =Х У

1 1

О. 1

1 1

1 1

1 1

3 ,6 записи, а шины 11 второго операндаI °

"через отверстия 5 опроса, при этом начала шин 12 первого операнда и второго 13

:операнда объединены и присоединены к соответствующему формирователю первого 1 и второго 15 операнда, а концы шин 16 и

17 первого н второго операндов через се-, лектирующие диоды 2 объединены и npuco-, l единены к соответствующему формировате-; лю младшего разряда адреса l. Формирователи 18 разрядного тока запрета присоединены к соответствующим шинам 19 разрядного тока запрета, которые прошиты через отверстия 6 записи каждой числовой, линейки 7 по каждому разряду в отдельно сти. Концы разрядных. обмоток 20 запрета через ограничительные резисторы «1 при-:

) I соединены к минусу источцика питания (ИП). Шины 22 считывания по каждому разряду в отдельности присоединены к со- .ответствующему усилителю 23 считывания.

Предлагаемое ЗУ, кроме функции записи, хранения и выдачи информации, может вы-, \ f б полнить и логические операции, такие как конъюнкция, дизъюнкция и равнозначность двух высказываний. Ъ

При этом любая(:. операции требует два .микротакта. Принцип работы и выполцение;

16 . устройством логических оиерацнй поясня-, ется таблицей, где 1 - импульс тока на.шине первого операнда; 1 — нм1 ! пульс тока на шине второго операнда;

15 g - импульс тока на шине. разрядзапр.

" ного гока запрета I, — импульс

I опр. тока на шине опроса; и И вЂ” сигнал, з. д. с, на шине считыванйя

481988, В качестве примера рассмотрил выпол- нение ЗУ операции конъюнкции, при этом сигнал на шине примем за 1, а его отсутствие за "0". а. Пусть в микротакте t. I =О, =0 и I =1. При данных услоу (запр. ) виях участок ферромагнитного материала вокруг отверстия записи будет перемаг- „ ничен по направлению против часовой стрелки. В следующий микротакт t . + 1

= 1 и J. = 1, в результате, опр. запр. которых участок вокруг отверстия опроса также будет перемагничен по направлению, . против часовой стрелки и сигнала э.д.с., на шине считывания не будет т. е. И- ==О. г б. При t когда 1 = 0, х у или 1 =1, 1 =0 .и $ =-1. Магх у запр. нитные «отоки о импульса тока любого операнда и от разрядного тока запрета взаимоскомпенснруются и в следующем микротакте ф. сигнала э.д.с. на шине считывания не будет (И =О).

При 1 = 1 1 =1 и х у запр.

= 1 магнитные потоки от разрядно1 о тока запрета и одного операнды взаимокомпенсируются, а импульс тока другого операнда (допустим первого) создаст магнитный, поток, который перемагнитит участок вокруг отверстия записи по направлению часовой стрелки.

В следующий микротакт

1 )+1

= 1 и 1 = 1 магнитный поток опр. запр. перемагнитит участок вокруг отверстия опроса по напр;1влепию против часовой стрелки. В результате этого появится сигь нал э.д.с. на шине считыва«ии И == l, «-

z ким образом будет выполнена операция

2;=x-у.

Предмет изобретения

Запоминающее устройство, содержащее накопитель на числовых ферритовых лнней1О ках с отверстиями записи и опроса, прошитыми соответственно, шинами считыва«ия, разрядного тока запрета и oEipoc«, «ричем каждая шина опроса проши;га через отверстия опроса в прямом направлении по каж дому адресу в отдельности, формирователи адресных и разрядных токов и усилители считывания, подключенные к соответствую щим обмоткам, и селсктирующие диоды, отличающееся тем,что,с

20 целью расширения функциональных возл1омакстей, оно содержит формирователи младшего разряда адреса, формирователь старшего разряда адреса и формироватеди первого и второго операндов, подключенные соотвеч25 ственно к началам шин первого и второго операндов; каждая шина опроса прошита дополпительно через отверстия записи в обратном направлении по каждому адресу и отдельности, начала шин опроса через се30 лектирующие диоды соединены с соответствующими форл1ирователями младшего разряда адреса, а концы шин опроса «одключены к формирователю старшего разряда адреса; ш цны первого и второго операндов

35 прошиты соответственно через отверстия записи и отверстия опроса всех числовых ферритовых линеек по каждому адресу в отдельности, причем концы этих шин через селектнрующие диоды соединены. с соответ40 с в

cTB lIIHMEI формирователял1н младшего Раз-, ряда адреса.

481938

Составитель E. ЗтадимиРов ива, и а (Тираж 648 Подписное

Заказ ÇÎÜ6

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, И3035, Раушская наб., 4

Предприятие сПатент», Москва, Г-59, Бережковская наб., 24

Редактор Я Гончвр Техред НД(анеева Корректор О.Тюрина