Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

бнбпйютен ;й А

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 482002 (61) Дополнительное к авт. свид-ву (22) Заявлено 11.08.72 (21) 1820023/26-21 с присоединением заявки № (51} М. Кл. H 03к 1Wu2 (63) УДК 681. 325 (088.8) Государственный комитет

Сонета Министров СССР по делам нзооретений н открытий (23) Приоритет (43) Опубликовано 25 08.75Бюллетень ¹31 (45) Дата опубликования описания12, 11.75 (72) Авторы изобретения

Б. В, Новоселов, И. С. Задорожный, В. И. Платанный и А. И. Шашц и (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД

Изобретение относится к дискретно; аналоговой вычислительной технике, а именно к частотно-импульсным системам, и может быть использовано в электронных радиотехнических и измерительных установках, в частности для контроля различных объектов и процессов, информация о состоянии которых поступает от частотных датчиков

Известен преобразователь частоты в код, содержащий реверсивный счетчик, двоичный умножитель, делитель частоты и вычитающее устройство, причем первый вход вычитающего устройства связан с входом преоб- @ разователя, а второй вход с выходом двоичного умножителя, первый выход вычитающего устройства подключен к знаковому разряду реверсивного счетчика, выходы которого связаны с одними входами двоичного 90 умножителя, другие входы двоичного умножителя соединены с выходами делителя частоты эталонного генератора, выходы реверсивного счетчика связаны с выходом преобразователя. 25

Однако известное устройство имеет не-достаточно высокое быстродействие. . Наблюдательное время переходного процесса такого преобразователя равно

7l,=, Ыб )

=2"

О где П, — количество разрядов реверсивного счетчика, — опорная частота двоичного умно=

0 жителя, Е, 1 — величина, характеризующая окон— чание переходного процесса. аделью изобретения является увеличение быстродействия преобразователя.

Йля этого в преобразователь введены сравнивающее устройство и логический элемент для переключения входных сигналов, входы которого подключены к входу преобразователя, к выходу двоичного умножителя к второму вйходу сравнивающего устройства, к выходу сравнивающего устройся ва, выход логического элемента связан со счетным входом реверсивного счеечика, второй выход вычитающего устройства связан с

482002

4 первым входом сравнивающего устройства, разователь частоты в код разомкнут по

Второй вход которого соединен с предпослед- ошибке. ним pàçðèäoì делителя частоты, На вход реверсивного счетчика 5 постуИзобретение пояснено чертежами. пает входной сигнал или сигнал обратной

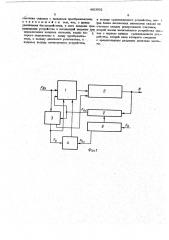

На фиг. 1 п ве ф ° риведена структурная элек- 5 связи через элемент И 1-2, открытый вытрическая схема преобразователя; на фиг. соким потенциалом с другого выхода срав2 — частично частично принципиальная электрическая нивающего устройства 4. схема преобразователя. Если рассогласование У p Q, то

Р р атель частоты в код содер- на суммирующий вход реверсивного счетВХ OC .™ жит логический элемент 1, це еключающий

Р лючающи g чика 5 поступают колебания входной частовходные сигналы, котоРый своими входами ты через элемент И 1-4, открытый потенсвязан с входом преобразователя частоты

1 циальным выходом вычитающего устройства в код, с выходом двоичного множителя 2, д д ч го умножителя 2,, 3, если Рассогласование g -g <(j, то на с выходами вычитающего устройства 3 и

Вх 0с вычитающий вход реверсивного счетчика 5 сравнивающего Устроиства 4, э выход свЯ- дб поступают колебания с частотой Обратной зан с входом реверсивного счетчика 5. связи с двоичного умножителя 2 через элеУправляющие входы реверсивного счетчика И 1 3 1й мент —, открытый вторым потенциаль5 связаны с потенциальными выходами вы-, ным выходом вычитающего устройства 3. читающего устройства 3. Импульсами входной частоты или чаВыходы реверсивного счетчика 5 связа:-. чп стоты обратной связи набирается на выхоны с входами двоичного умножителя 2, де двоичного умножителя 2 частота, близпреобразующего код в частот об атной тоту обратной кая к входной. В этом режиме преобразосвязи. ватель работает, как статический, обладая .

Другие входы двоичного умпожителя 2 при этом бо б и и этом ольшим оыстродействием. соединены с выходами делителя частоты 6. К огда ошиока между входной частотой

Выход двоичного умножителя 2 соединен и частотой юратной связи станет. меньше с одним из входов вычитающего устройства е Ото некоторои наперед заданной малой частоты

3, другой вход которого соединен с входом У <Р х х О, тс элемент 1-1 откроется, а преобразователя, элемент И 1-2 закроется потенциалом с

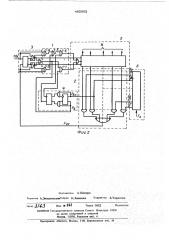

Выход вычитающего ст ойства 3 соединен с входом сравнивающего устройства Разователь замыкается по ошибке и превра4, второй вход которого соединен с одним шается в следящую систему с астатизмом из выходов делителя частоты 6 первого порядка в установившемся режиме. лок 1 логических элементов содержит Если считать, что переходный процесс р лемента И 1 1, як заканчивается при переходе преобразовате— ля в следящий режим, так как воздействие соединенные так, что входы элемента д лемента И достаточно мало, то наблюдательное .

1 4 связаны с вхо ом п есб з д р сбразователя время переходного процесса преобразовате0 частоты в код и с потенциальным выходом ля равно ! вычитающего устройства 3. Входы элемен — 4О

fL

m И 1 — 3 связаны с выходом двоичного умножи". еля 2 и с другим потенциальным

Н

Р {) выходом вычитающего устройства 3. Вы- П олучаем выигрыш в быстродействии в ходы элементов 1-3 и 1-4 соединены с щ, раз. входами элемента ИДИ 1-5. Входы эле- 4й мента И 1-2 соединены с выходом эле- П I

Предмет изобретения мента ИИИ 1-5 и с одним из выходов ср, внииающе|-о устройства 4, входы эле- Преобразователь частоты в код, < одермента И 1-1 соединены с импульсным жащий реверсивный счетчик, двоичный умноВыходом вычитпощего-усгройства 3 и с бО житель, делитель частоты и вычитающее вторым потенциальным выходом сравниваю- устройство„причем первый вход Вычитающего устройства 4. Выходы элементов И

3 -1 1- щего устройства связан с входом цреобраи .-2 соединены с входом Реверсив;— нм о счетчика 5,. зователя, а второй вход — с выходом двоичНОРО умнОжителя первый выход Вычита еще

flf >l.обРазОВатель частоты B Kод рабо- 55 чает следующим образом. го устройства подключен к знаковому разП ряду реверсивного счетчика, выходы котори большой ошибке между входным Рого связаны,с.одними входами двоичного и Выходным воздействиями g ) f эле1 У вЂ” умножителя, другие входы двоичного умцожимецт П 1-1 закрыт низким потенциалом .тели соединены с выходами делителя час ты, < о сравнивающего устройства 4 и преоб- бО р — эталонного генератора, выходы реверсивного

481002

5 счетчика связаны с выходами преобразователя, .к выходу сравниваюшего устройства, вью т л и ч а ю щ и Э с а тем, что, с целью . ход блока логических элементов связан со увеличения быстродействия, в него введены сра- счетным входом реверсивного счетчика, внивающие устройство и логический элемент для второй выход вычитаюшего устройства свя —.. переключения входных сигналов, входы ко-.- 5 зан с первым входом сравнивающего устторого подключены к входу пресбразова- ройства, второй вход которого соединен геля, к выходу. двоичного умножителя, к:, с предпоспедним раарядом делителя часто- в горому выходу вычитаюшего устройства, ты.

482002

Г

Составитель А.Шапиро редактор А.3иньковскивТекред Н.Ханеевн норректоР 3.Tapacooa . -дакад, !фД Над. )4 9И Тираж. 902 .: Подписное .

UlGfHIIH Государственного комитета Совета Министров СССР ,по делам изобретений н открытий

Москва, 113035, Рвушская наб., 4

Предв сПатент, Москва, Г-59,. Бережковская наб., 24