Устройство для обнаружения сбоя цикловой синхронизации в системах передачи данных с последовательным декодированием

Иллюстрации

Показать всеРеферат

- °

| 6льс; иЛ

О П И С А Н И Е («) 482024

ИЗОБРЕТЕ Н ИЯ

Союз Советских

Социалистических а еслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заявлено 20. 12.72 (21) 1860965/26-9 с присоединением заявки № (23) Приоритет (51) M. Нл.

Н 04 1, 7/08

Гасударстаанни|й комитет

Соавта Иииистроа СССР

Il0 делам изабратоний и откра(тий

Опубликовано 25.08.75Бюллетень 1ио 31

Дата опубликования описания 15. 10. 7 5 (М) Удк

62 1. 394. 662. . 2 (088. 8) (72) Авторы изобретения

Н. А. Александров и Ю. Н. Мартин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СБОЯ

ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЫХ

С ПОСЛЕДОВАТЕЛЬНЫМ ДЕКОДИРОВАНИЕМ

1 Я

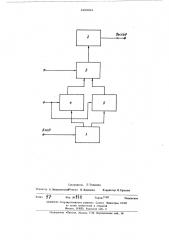

Изобретение относится к технике свя- На чертеже приведена структурная элекзи, а именно к технике передачи информа- трическая схема устройства. Устройство ции с последовательным декодированием. для обнаружения сбоя цикловой синхрониИзвестно устройство для обнаружения зации в системах передачи данных с посбоя цикловой синхронизации в системах к следовательным декодированием, содерпередачи данных с последовательным де- жит пороговые элементы 1 и 2, вход покодированием, содержащее пороговые эле- рогового элемента 2 соединен с выходом менты и накаплИвающий сумматор. накапливающего сумматора 3, первый выОднако известное устройство обладает ход порогового элемента 1 соединен с большим временем обнаружения сбоя цик- |0 первым выходом элемента И 4, а второй ловой синхронизации. выход - с первым входом элемента И 5, Целью изобретения является сокращение выходы элементов И 4 и 5 соединены с времени обнаружения сбоя цикловой син первым и вторым входами сумматора 3 хронизации при заданной вероятности лож- соответственно. Вход порогового элеменного обнаружения сбоя. 1а та 1 является входом устройства, выход

Для этого выходы первого порогового порогового элемента 2 является выходом элемента, вход которого является входом устройства. устройства, подключены к одному из входов двух элементов И, на другой вход ко- Устройство работает следующим обраторых подан сигнал переполнения декоде- 20 ра, а выходы элементов И через накапли-,,На вход поРогового элемента 1 постУваюший сумматор, управляемый сигналом пает из последовательного декодера код успешного декодирования, подключен к С положения указателя. На объединенные входу второго порогового элемента, выход вторые входы элементов И 4 и 5 постукоторого является выходом устройства. « И пает из декодера сигнал переполнения де-

482024 кодера, на третий вход сумматора 3 по- - ступает сигнал успешного декодирования.

При успешном декодировании сигнал успешного декодирования, поступающий на третий вход сумматора 3, устанавливает его в нулевое положение. Код С положения указателя, поступающий на вход устройства, постоянно сравнивается с выбранным порогом П порогового элемента 1.

При С (П формируется сигнал на первом

10 выходе порогового элемента 1, при С $ П формируется сигнал на втором выходе тоI .ro же порогового элемента.

На первый или второй входы сумматора 3 сигналы, формируемые пороговым элементом 1, поступают через элементы И 4 или И 5 при переполнении декодера (при поступлении сигнала переполнения декодера на объединенные вторые входы элементовИ4 и5).

При поступлении сигнала на первый вход сумматора 3 к его содержимому прибавляет-. ся константа Ь, при поступлении сигнала

1 на второй вход сумматора 3. — прибавляется константа Д, причем Ь ) Д, О.

Сигнал на выходе устройства формируется, если содержимое накапливаю пего сумматора 3 превысит выбранный порог П поро2 гового элемента 2. Значения порогов П

1 и П устанавливают из условия минимального времени обнаружения сбоя синхронизации при обеспечении заданной вероятности ложного обнаружения сбоя.

Предмет изобретения

Устройства для обнаружения цикловой синхронизации в системах передачи данных с последовательным декодированием, содержащее пороговые элементы и накапливаю-! шиисумматор, отличаю шеес я тем, что, c:öåëüþ сокращения времени об-, наружения сбоя цикловой синхронизации при заданной вероятности ложного обнаружения сбоя, выходы первого порогового элемента, вход которого является входом устройства, подключены к одному из входов двух элементов И, на другой вхоц которых подан сигнал переполнения декодера, а выходы элементов И через накапливаюший сумматор, управляемый сигналом успешного декодирования, подключен к входу второго порогового элемента, выход которого является выходом устройства.

482024

Изд. KЦ3 Тираж 740 Подписное

Заказ

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, l3035, Раушская паб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24

Составитель Г.Те лова

Редактор А.ЗиыьковскийТекред H.Ханееви Корректор ft.Орлова