Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ к лвтовскомв свидвтвльствт

482737

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву— (22) Заявлено 06.04.73 (21) 1904430/18-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 30.08.75. Бюллетень № 32 (51) М. Кл. G 06f 7/04 гасударствеивый комитет

Совета Министров СССР по делам ивааре;е!!ий и открыт!!й (53) УДК 681.332.65 (088.8) I Дата опубликования описания 21.07.76 (72) Авторы изобретения

A. Д. Подлиннов и II. H. Маторин (71 ) Заяви Гель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Устройство относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики и контроля.

Известны устройства для сравнения двоичных чисел, содержащие регистр. Выходы разрядов регистра соединены с соответствующими установочными входами двоичного счетчика, счетный вход которого связан с входной шиной устройства, а выход последнего разряда — с входом установки в единичное состояние триггера знака. Инверсный выход триггера подсоединен к одному из входов первой схемы «И», а прямой выход — к одному из входов второй схемы «И», другой вход которой подключен к выходу переноса соответствующего нижней границе допуска разряда двоичного счетчика, а выход — к входу установки в единичное состояние триггера памяти.

Прямой выход триггера памяти связан с одним из входов третьей схемы «И», инверсный — с одним из входов четвертой схемы

«И», другой вход которой соединен с прямым выходом триггера знака, а другие входы первой и третьей схемы «И» и третий вход четвертой схемы «И» — с шиной управления, которая через схему задержки подключена к входам установки в нулевое состояние тригге1т я I:а х я т и > т р и Г f p 2 3! а к а и 13 е Г ! с т1т а . В и 3 В е стнос устройство введен» ll пятая схема «И».

Известные устройства допускового контроля не позволяют анализировать аномальные выбросы оцениваемого параметра, которые необходимы для устройств контроля и диагно5 стики неисправностей.

Цель изобретения — расширение класса решаемых задач.

Для этого в устройство для сравнения двоичных чисел введен дешифратор сбоев, состот0 ящий нз двух схем «И», схемы «ИЛИ» и двух триггеров, входы установки в нулевое состояние которых связаны с выходом схемы задержки, вход установки в единичное состояние первого триггера — с выходом первого разря15 да двоичного счетчика, а вход установки в единичное состояние второго триггера — с выходом первой схемы «И» дешифратора сбоев, один из входов которой соединен с прямым выходом триггера знака, а другой — с выхо20 дом переноса соответствующего верхней границе допуска разряда двоичного счетчика.

Прямой выход второго триггера подключен и одному из входов схемы «ИЛИ», другой вход которой связан с выходом второй схемы «И»

25 дешифратора сбоев, входы второй схемы

«И» — к инверсным выходам первого триггера и триггера знака соответственно, а выход схемы «ИЛИ» — к одному из входов пятой схемы «И», другой вход которой соединен с

30 шиной управления.

482737

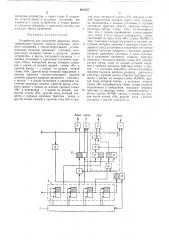

Блок-схема устройства представлена на чертеже.

Устройство содержит регистр 1, двоичный счетчик 2, схемы «И» 3 — 7, схему 8 задержки, триггер 9 памяти, триггер 10 знака, дешифратор 11 сбоев, включающий в себя логическую схему «И» 12, триггеры 13, 14, схему «И» 15, схему «ИЛИ» 16.

До начала измерений в регистр 1 вводится поправка, соответствующая нижней границе изменения измеряемой величины, т. е. равная разности между эталонным значением этой величины (N„) и допустимым отклонением (Л=2" )

На счетный вход двоичного счетчика 2 поступает число-импульсный код (У„,„, ), соответствующий измеряемой величине. Так как поправка введена в двоичный счетчик в обратном коде, происходит ее вычитание из N „„, после чего проводится анализ состояний соответствующих разрядов двоичного счетчика, Значение допустимого отклонения (A=2 > ) определяется выходом i-ro разряда счетчика.

По окончании последовательности импульсов N „,,„в двоичном счетчике формируется . код разности между эталонным (заданным) значением N„, и N„,„Если последовательность импульсов У„,„,, поступившая на двоичный счетчик, меньше нижней границы поля допуска, то сквозной перенос в двоичном счетчике не формируется, триггер 10 знака остается в исходном нулевом состоянии и onрос схемы «И» 7 управляющим импульсом подает сигнал «Ниже». Сигнал «Сбой» формируется, если нет переноса с первого разряда двоичного счетчика, при этом триггеры 13 и

10 остаются в исходном состоянии и схема «И»

15 выдает сигнал, который через схему «ИЛИ»

16 открывает вентиль для прохождения управляющего импульса на выход «Сбой».

Когда N „,„находится в поле допуска, появляется сквозной перенос, который устанавливает триггер 10 знака в единичное состояние, при этом триггер 9 памяти остается в исходном нулевом положении, так как схема

«И» 3 открывается после обнуления двоичного счетчика 2 сквозным переносом, а перенос с

i-го разряда после этого не формируется. Схема «И» 5 выдает сигнал «Норма» за счет совпадения единичного и нулевого выхода триггеров 10 и 9 соответственно.

Если N „„.„, превышает поле допуска, с выхода i-го разряда возникает перенос, который устанавливает триггер памяти в единичное состояние, и схема «И» 4 подает сигнал «Выше».

При дальнейшем увеличении У„,„появляется перенос с j-го разряда двоичного счетчика, что фиксируется триггером 14, который устанавливается в единичное состояние через схему

«И» 12, выход единицы триггера 14 через схему «ИЛИ» 16 выдает разрешение на формирование сигнала «Сбой» схемой «И» 6.

Таким образом, фиксируются все входные ситуации, возникающие при сравнении двух двоичных чисел. б

25 зо з5

4

При значениях У„„,-: (У „ — Л) после окончания цикла сравнения триггер знака остается в нулевом (исходном) состоянии, выдавая с помощью логической схемы «И» 7 в момент прохождения управляющего импульса выходной сигнал «Ниже» нормы.

При значениях У „„, ) (У„+Л) после окончания цикла сравнения триггер знака переходит в единичное состояние, закрывая схему «И» 7 и открывая по одному из входов схему «И» 3, Импульс переноса с i-го разряда, соответствующий превышению верхнего допуска, через схему «И» 3 устанавливает триггер памяти в единичное состояние, фиксируя с помощью схемы «И» 4 в момент опроса выходной сигнал «Выше» нормы.

При значениях (N„— Л) (У „,„, ((N„+Л) по окончании цикла сравнения триггер знака также занимает единичное состояние, запрещая формирование сигнала «Ниже» нормы и открывая по одному из входов схемы «И» 3, 5, но очередного переноса с -ro разряда двоичного счетчика после переключения триггера знака уже не возникает, так как по условию

У „„, <(N„+a).

Таким образом, триггер памяти остается в исходном (нулевом) состоянии, а на выходе логической схемы «И» 5 в момент опроса появляется выходной сигнал «Норма».

Аналогичным образом, анализируя состояние любых других разрядов двоичного счетчика (1>,..., i ..., 1,..., а,) можно вести оценку любых отклонений параметра N„,„

В частности, с помощью дешифратора сбоев по состоянию первого и j-го разрядов счетчика проводится анализ анам альных выбросов (сбоев).

При значениях N„„,)) (У„+Л) формируется перенос с одного из старших разрядов (i ð ) счетчика разности, который через открытую ранее схему «И» 12 устанавливает триггер 14 в единичное состояние. В свою очередь выход триггера 14 выдает разрешение через схему «ИЛИ» 16 на схему «И» 6, через которую в момент прохождения управляющего импульса формируется сигнал «Сбой». Наличие при этом сигнала «Выше» нормы позволяет однозначно характеризовать отказ (например, У„,„поступает в виде непрерывной последовательности) .

При вырожденном (вплоть до одного импульса) значении входной импульсной последовательности N „„,(((N „— Л) триггер 10 знака и триггер 13 остаются в исходном (пулевом) состоянии и открывают схему «И» 15, выходной сигнал которой через схему «ИЛИ»

16 и схему «И» 6 подается на выход устройства в виде сигнала «Сбой».

Наличие при этом сигнала «Ниже» нормы позволяет сделать вывод о частичном или полном пропадании импульсов измеряемой последовательности.

Синхронизирующий работу всего устройства управляющий импульс опрашивает одновременно схемы «И» формирования выходных

482737

Выше Ноута Сеай

Н4/Же

5 сигналов устройства, а через схему 8 задержки устанавливает в исходное состояние все элементы и узлы устройства, а также вводит нз регистра поправку в двоичный счетчик для каждого цикла сравнения.

Предмет изобретения

Устройство для сравнения двоичных чисел, содержащее регистр, выходь! разрядов которого соединены с соответствук щими установочными входами двоичного счетчика, счетный вход которого связан с входгой шиной устройства, а выход последнего разряда — с входом установки в единичное состоян! е триггера знака, инверсный выход которого соединен с одним из входов первой схемы «И», а прямой выход — с одним из входов второй схемы «И», другой вход которой подключен к выходу переноса соответствующего нижней границе допуска разряда двоичного счетчика„ а выход — к входу установки в единичное состояние триггера памяти, прямой выход которого связан с одним из входов третьей схемы

«И», а инверсный — с одним из входов четвертой схемы «И», другой вход которой соединен с прямым выходом триггера знака, а другие входы первой и третьей схем «И» и треб пш вход четвертой схемы «И» связаны с шиной управ чеппя, которая через схех! 1 задержки подключена к входам установки в нулевое состояние триггера памяти, триггсра знака и регистра, пятую схему «И», отли тющееея тем, что, с целью расширения класса решаемых задач в него введен дешифратор сбоев, состоящий нз двух схем «И», схемы «ИЛИ» н двух триггеров, входы установки в нулевое со-!

О стояние которых связаны с выходом схемы задер>кки, вход установки в единичное состояние первого триггера соединен с выходом первого разряда двоичного счетчика, а вход установки в единичное состояние второго триггера !

5 соединен с выходом первой с;емы «И» дешифратора сбоев, один из входов которой соединен с прямым выходом триггера знака, и другой — с выходом переноса соответствующего верхней границе допуска разряда двоичного

20 счетчика, прямой выход второго триггера. соединен с одним из входов схемы «ИЛИ», другой вход которой связан с выходом второй схемы «И» дешифратора сбоев, входы которой подключены к инверсным выходам первого

25 триггера и триггера знака соответственно, а выход схемы «ИЛИ» связан с одним из в.,одов пятой ехех!ы «И», другой вход которой соединен с шиной управле.!ия.