Импульсно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

„, 482883

Союз Советских «оциалистических

Республик (61) До«с)лиительиое к авт. свид-ву— (22) Заявлеио 29.06.72 (21) 1802733/26-9 с ирисосдииеиием заягки М— (23) Приоритет—

Опубг!вковано 30,08.75. Бюллетень М 32

Дата опубликования описав«я 29.03.76 (51) М. Кл. Н 03k 904

И 03(! 3. 04 (ооударственнн(й но(катет

Совета (Лииистрав СССР ло делам изобретений и открытий (53) УДК 621.376.55 (088.8) (72) Авт >pi>i

10, А. Додонов, 3. В. Марголис, В. П. Романов, Г. А. Соков и

Ю. Ф. Шпилев (71) 3«я>в«тес(» (54) ИМПУЛЬСНО-ФАЗОВЫЙ ДИСКРИМИНАТОР! I >ooJ>eicii»c отиосится к рад<и)тек«ическим усгройсзьам фазового срав«сиия и может испол;>R;>Ват»ся « системах фазо«ой автоиодстройки чл(тот!.<, «3«ример, в сии Гсзаторяк частот с цифровым умиожитслсм.

> и J! J(стс«импульс«о-(1)азов ый дискрим и илТ0Р, СО 1CJ))i(3 И(«й Д«3 ?7 Р33РЯД!Х счетчика имиульсoR и формирователь выходIiOI O СИП<3 13.

0;l I J 3!(о «и 3 В с с т и О > (м (т р О и с 1 В (и с В 0 3 м 0 ж,<о обеспечит» Jle(lpcp<>lt)II) ю зависимость уров-! i >(!! O C 1 O J< I I I: 0 Й С 0 СТ ?< В 1 и Ю Ш С и В I>I % 0. I < С) Г 0 С И Г«ял;> (и C(одиык ими,,tbCJI»IX иси.лсдовл.! ель«осте(<.

Цел(. ><Зобрстсиия — обесиечеиие исирерьи«oJl: л Jl(им«с<и тров«я «Ос. To(«1<1()lf составля><<(et, <: Iu);( U J>t. COÄJ JOÃO СИ Г-!! 3 Л с! Р I >! И О. 1!! C. > и В! < д С,1 0 Г И Ч C c. К O и С ." С З < 1>(Р Ы—

>итлиия, «кл(очл(ои(сй и — -1 ло(ическик схем 20 займя сд<<иицы старшего рлзрядл, едииичиыс !

i иулс«ыс В»<хо (ы каждой lip(. 1ыдущей из коI ÎP!>(.;. (ОС;И «СИЫ С СООТВСТС > IJ> lotll«)>It! ИМ В>0дами «осле.()юи(сй, л c;((I

«ыхолы; 0(л(.(;(ей лоп<чсской схсмы злйма 25

С;(<i Ст(1 РШС ГО Pc<3 Р)1, (Л (ОС, (i<(i ll ы С (. 001 «ст(-< «уlolli (I)OP)<1< POI)c! ! (lC 1»ÑОВ, C (11111?ЧII»ie II ИХ ЛС- ЗО выс В(.!ходы каждого из ?7 — 1 разрядов обои.х счетчиков соедииеиы с соответствующими им

I»XO. I 3 Ç<È КЯЖДОИ Из (OOTBC1 СТВ > !0(I<. ИО IIO)<ср) )?- — 1 лОГИ <сских с:>ем зяйм)1 е;(< старшего разряда формирователя вы.;од(юга сип<аля, 3 едииичиыс и нулевые в(<ходы иоследш(к л-ых разря lot) обои.; счетчиков сосдииеиы с соответствую«(ими Входами выкод-!

<0<1 логической схем(< форм«рова««я Ieêóùcro зилчеиия и-fo старшего (вои i!to(0 рязрядл разности состояний счетчиков.

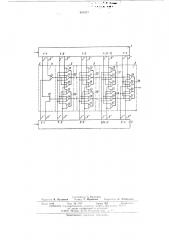

113 чертеже изооря)кеия ())у«кциои(<Г<»и?)я с (см3 импульсно-фазового дискримииатора.

Дискриминатор содержит два ??-рлзрядиы . дво!<чи»(х счетчика и 2 импульсов, и формироватсль 3 «»(ход«ОГО с«ГI< 3 13, состоя lции 1>з

?7 — -1 лоп<ческик с.;ем 4, 5, 6, 7 займя сдииицы старшего разряда и выход«ой лоп(чсской схемы 8 формирования текущего зиачеиия

?7-ГО старшеГО дВО«ч«ОГО рязрядя раз«ости состояиий счетчиков импульсов, причем логические схем»(4. 5, 6, 7, 8 включают в себя с.;емы 9 — -31 coi;(!3lettt

32 — 39.

Устройство работает слсду(ошим образом.

II3 входы ?7-разря l«I>!It<>lx счетчиков

1 и 2 импульсов поступают соотги)тстч)еиио сравииваемые ио фазе имиульси»ц последовательности. Сигиялы единичны.; «1» и пулеBt>1x «0» вы)(одов каждого p3. р Jt(1 Обоих счетчиков 1 н 2 поступают на формирователь выходного сигнала 3, работающий в ре5киме непрерывного вычитания двоичных чисел в дополнительном коде и организованный по принципу последовательного формирования единицы займа из соседного старшего разряда с помощью логическик с|ем 4, 5, 6, 7 н формирования текущего значения и-ro старшего двоичного разряда разности состояний счетчиков импульсов с помощью выкодной логической скемы 8.

При наличии единичных уровней сигналов с соответствующих единичнык «1» и нулевых

«О» выходов первы| разрядов обоих счетчиков 1 н 2 на обоих входах схемы 9 совпадения на единичном «1» выходе логической схемы 4 займа единицы старшего разряда возникает единичный уровень снп1ала. B противном случае сигнал единичного уровня формируется на пулевом «О» вы|оде логической скемы 4 с помощью собирательной с:|емы 32.

Прн наличии едшшчпык уровней сигналов с соответствующих единичных «1» н нулевых

«О» выходов ьторык разрядов обоих счетчиков и логической схемы 4 займа единицы старшегo разряда на в|одах котя бы одной из с|ем

10, 11, 12 совпадений, на выходе собирательной скемы 33, являющимся единичшям «1» выкодом логической скемы 5 займа единицы старшего разряда, возникает единичный уровень сигнала. Ь противном случае снп1ал единичного уровня формируется с помощью схем

13, 14, 1о совпадения и собирательной скемы

34 на нулевом «О» выходе логической с емы 5.

Формирование единичного уровни сигнала на единичном «!» If пулевом «О» выкодак логической с|емы 6 займа единицы старшего разряда с помон1ыо схем 16 — 21 совпадения н собнрательнык скем 35, 36 н логической с. емы 7 займа единицы старшего разряда с по- .If) мощью скем 22 — 27 совпадения и собирательны| скем 37, 38 аналогично формированию единичного уровня на выхода| логической скемы 5.

Прн наличии еди1шчнык уровней сигналов -15 с cooTBOTcTB3.follfflx единичны| «1» и нулевык

«О» f3f>IxofoB п-и| разрядов обои., двоичны| счетчиков 1 и 2 и логической с емы 7 за11ма сдиш3цы старшего разряда па в|оде котя бы

4 одной из схем 29 — 31 совпадений, на выходе собирательной схемы 39 возникает единичный уровень сигнала, а в противном случае на выходе собирательной cxeiif f I 39 возникает нулевой уровень сигнала.

Таким образом, на выкоде импульсно-фазового дискриминатора формируется периодическая последовательность единичнык и нулевых уровней, структура которой определяется временным сдвигом между входными импульсными последовательностями и видом их неравномерности. Зависимость уровня постоянной составляющей на выходе импульснофазового дискриминатора от фазового сдвига между вкодными импульсными последовательностями имеет непрерывный характер.

Предмет изобретения

Импульсно-фазовый дискриминатор, содер жащий два и-разрядных двоичных c>lcT>IIIIXI импульсов н формирователь и входного сигнала, от.1ичаюи ийся тем, что, с целью обеспечения непрерывной зависимости уровня постоянной составляющей выходного сигнала, формирователь выходного сигнала выполнен B виде логической схемы вычитания, включающей п— 1,логических схем займа единицы старшего разряда, единнчныс н нулевые вы. коды каждой предыдущей нз которых соединены с соответствующими нм вкодамн после. дующей, а еднничныс и пулевые выходы по. следней логической схемы займа c;I IIIIIIIII» старшего разряда соединены с соответствую щимн входами выходной лопшеской схемf> формирования текущего значения п-го стар. шего двоичного разряда разности состояний счетчиков импульсов, единичные н нулеияс выходы каждого нз и — разрядов ооонх счетчиков соединены с соответствующими нм 13кодамн ка5кдой нз соответствующн. по номеру

n — 1 логических схем займа eqllfflf«1>f старшего разряда формирователя выходного сигнала, а единичные н нулсвьн. и.1ходl>l нослсдннк

n-I>fx разрядов обоих счетчиков соединены с соответствующими входамн выходной лоп11cской схем ы фо!эм н рованпя текуп1еГО зна 11 Illfл

l1-BО CTBPfIlCCO 7 f3O1f I1IOI O Pff3P5f l<1 PBBIIOCTН С0стояний счетчиков. (.осTBI

Рсдак гор В. Булдаков Текред T. Миронова 1<орр< к i о; JI. ) .ение«

Заказ 79-10 Иод. No !737 !и!)авс 902 1!иди<.с«о<

1!НИИ!1И l <осударствснного ко!»!<< ;< Совета .

1130 15, Москва, Ж-:35. Рм<н к«я а0,. д. -!

Череповецка!i городска,«ии I !ннн, н