Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

(» 482889

Оп HCAHHE

ИЗОЬРЕТЕН ИЯ н лбтОРснОы СвидЕтбйьСТВМ

Союз Советских

Социалистических

Республик (61) Доно IIIIITc Ibltîå к аит. свид-ву-(22) Заявлено 12.04.72 (21) 1772470 26-21 с присоеди заявки №вЂ” (?3) Приоритет—

Опубликовано 30.08.75. Бк)ллетепь № 32

;)ята опубл||коваиия описания 03.02.76 (01) М. 1,л. Н 03k 13 17

Гасударственный комитет

Совета Министров СССР но делам иоооретений и открытий (5, 3) УД)5, 681.325(088.8) (72) Автop ы изобретения

В. С. Плеханов и В. М. Сидоров (7!) Заявитель

Новосибирский электротехнический институт (()4) АНАЛОГО-ЦИФРОВОЙ П Р ЕО БРАЗОВАТЕЛ Ь! 1:IO()p(. т(il llc Отпос|ГI (51 l< в1 п(исгlи l сльиои

1 С. < II ИКС tl 110)КСТ ИСПО.1ЬЗОВ(1Т ЬСЯ Д 1 и ПОС| POсиия много! Llltÿë0èûõ lllaлого-((ифров(,(х преобразователей си(те)! автомaòè÷åñêîãî

I(0IITPOЛЯ.

Известен «палого-цифровой преобрязовагель соДеРжЯЩий геllCPrlToP;(I!01! Itto-yOblaalon(сй Iloc.!c;LOIIaòcëû,î T!i llìíóëüñîè напряжения, оперяLLIIDllïûé усиг!итель, зяпомиtta!OIILèé

l<()II;L0IiCr1T0P, i<0Ì!13Р!!ТОР, ДВЯ ПСРЕК. ИО )ЯТСЛЯ, логическое устройство, схему управления и

CII II

КО М !|3 Pal TOPrl СОЕДИИЕИ (. ЛОГИ 1ЕСКИ М ) CTPOII (..твом, ив|ход сипхроиизирующсго генератора сосдппеп со входом схемы управления, выходы которой соединены со входами логического устp011< гвя и генератора двоичпо-убывающей последо|<атслы|ости импульсов папря)ксlllI51.

Цель изобрст lltt51 — — упро!цеиис схемы и Р ()() P3:I OH 3 ò(ë ß .

;)ля aT010 Oи 0;I(. P)!two;Lo(I зя| îмипяющего конденсатора, tIP11 Э . О )I Il Pß)l ОЙ ВХО Д ОП С Pal(ÈO III!OÃO МСИЛИ 1(. ля !Ср< .3 норма IbIIO замк!1утыЙ 1

О скос устройство соединен с уиравля!ощим ьходом второго управляемого переключателя.

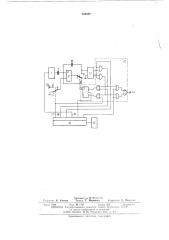

На чертеже изображена <1)упкциоияг!ьия51 схема преобразователя.

Аналого-цифровой преобразователь с по1:) слсдователы!ым поразрядным вычитанием эта lottllых напряжений из вход!юго напряжения содержит гецератор двоичпо-убывающей последовательности импульсов напряжения 1, !

<ото()ОГО через KoflдеисятОр 2 иoд20 ключеи и!|верс ый вход операционного усилителя 3. 1(другому входу усилителя 3 присос;(инеи переключаем ый контакт упра вляемого двухпозиционпого перскгиочятеля 4, нормальI10 334tl

Выход операционного усилителя 3 соед1)нец с переключаемым контактом второго управляемого переключателя 7. Нормально замкнутый 30 8 п нормально разомкнутый 9 контакты пере3

482889!

15 0 ключяпгеля 7 сосд)!Иеllbl с инверсным входом усилителя 3, причем первый соединен !!епо(редствеп);о. я второй — черсз 3;tt)n»ппаюf! l I! Й ко 1;1 е f i Г я то 1) ) li . 1 1 О j) i>,! 11:1 ы 0 р 1) 3 0 х l K l! >> т ы Й ! > О ) I Т 11 1(Т . ) «e P C i(, 10 и 1! 1 С. 11! r «O e, (I! I! (!1 Г 1! К Ж ( (0 вхОдох) КО 1!11 ря 1 0)) il 1 . 1)тОрОЙ в. Од Iio)! ! l I) P?iт0Р11 ! l i 0;l ii 1 !0 1(. 1! ii ООгцсЙ ш! Iп(, Я (>ГО выход — к логическому устройству !2. В1>!ход

13 логического устройства 12 сое;()п!еп с управляющим входом второго управляемого переключателя 7, а выход 14 логического устройства 12 является выходом преобразователя в целом. Выход cHiiKpoiiilaирующего генератора 15 соединен со входом управляющей схемы 16, у которой выход !7 подключен к логическому устройству 12 и к управляющему входу первого управляемого переключателя 4, выход 18 соединен с логическим устройством

12, а выход 19 — со входом генератора двоично-убывающей последовательности импульсов напряжения 1.

Преобразователь работает следующим образом.

Импульс, поступающий с выхода 17 схемы управлеиия 16, Bb13bIBaeT срябятывапис переключателя 4 и устанавливает логическое устройство 12 в исioJIHOc состояние. При этом

011ерЯцпоп и ый усилите1ь 3 ря ботЯет с коэффициентом передачи, раш!ым единице, и коп((ен(;ITop 2 от коптакта 6 перекгпочателя 4 и !Срез у cHëHTÐ1ü 3 зяряжяется до няпря)кеп1!я, ря в)!ОГО LKO (!10:>1у. По OKOII ) alt?ill 11)>>)п>> 7bCA

l!a выходе 17 переклиочятель -1 возвращается в исходное состояние и одновременно импульсом с выходя 18 схемы управления 16 вызывается импульс с выхода 13 логического ус1ройства 12, вызыва!ощий срабатывание пере>ключ ятсля 7, и заряд, )!BKQI)ëcif?iый В Iiollденсаторс 2, полностью передается в запоминающий конденсатор 10. После этого с выхода 18 схемы управления 16 в логическое устройство 12 Г(оступают импульсы опроса состояния компаратора 11. Если пяпря)кение на выходе преобразователя имеет отрицательное зпачепие, то на входе компаратора 11 напряжение положительно, и в этом случае, в ре3>> ьтяте oil poca состоя пия комп я ряторя 1 1, логическое устройство 12 на выход 14 выдает импульс, наличие которого фиксирует то, что пя входе преобразователя папряжепис отрицательно. Если напряжение па входе преобразователя поло)кительно> то это фиксируется отсутствием импульса иа выходе 14 логического устройства 12, которое реагирует, таким Oopaao)t, пя результат опроса состоя пия компаратора 1! при наличии пя его вхо25

15 0

55 дс î 1 риця)ельпого ни !! ря)кеiIIIH. 11м п л ь(01!роса состоя пия iio»t it a pa! Op a 1 1 за к?! Ич и в?)(."1 00011 ка)к I bi и i я KT f! ))co() PB30 Я ! > Я. Тll l; l>l ВЗВЕШ И В ?!!! ИЯ 1! i! (!) ОP .>! 11! (l! I! (!1!>l I! I l 1) I I I I и l

H>_#_0;jt lOI 0 П(! ПРЯ)К(>!и)Я If, I II (.. ГО OCTI!ТК?! ЭТ(! 1()li ного и()1!ряжеи!!я) till(lлоп! Illl>I ра«смотреп!и> л!У Я)СГУ 01IРЕДЕ, !(.ПИЯ 3!!Яii;1 ВХОДПОГО ПЯ! l!)иж I)Hsl и длятся в тече!)ис двух периодов следова!!ия импульсов сппхроиизирующего ге!)ератора 15. Перед каждым тактом взвешивания схема подготовлена к вычптапи)о, причем вычитание осуществляется но переднему фронту эталонных импульсов генератора 1, ссли И iia выходе усилителя 3 в моме?IT опроса предыдущего такта положительно, либо по зад!!ему фронту, если lie!liряжение пя выходе усилителя 3 в момент опроса предыдущего тя кта Отри ца тел ьпо.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий генератор двоично-убывающей последовательности импульсов напряжения, операционный усилитель, запоминающий конденсатор, два переключателя, логическое устройство, компаратор, схему управления и сипхронизирующий генератор, причем выход компаратора соединен с логическим устройством, выход сипхроиизирующего генератора соединен со входом схемы управления,-выходы которой соедипе lbl со входами логического устройства и генератора двоичпо-убывающей последовательности импульсов напряжения, отличаюи!ийся тем, ITQ, с целью упрошеиия схемы, он содержит конденсатор. один вывод которого соединен с выходом генератора двоично-убывающей последовательности импульсов напря)кения, я другой — с инверсным входом операционного усилителя и одним из выходов запоминающего конденсатора, при этом прямой вход операционного усилителя

«СРе3 HQPмально замк?!Утый KQHTBKT 1)СРВОГО управляемого перекл)очатсля соединен с оощей шипой, а через нормально разомкнутый контакт этого переключателя — с источником входного напряжения, кроме того, выход операционного усилителя соединен со входом второго переключателя, нормально Замкнутый контакт которого «Oczi<?tet! с инверсным входом операционного усилителя, я нормальIIo разомкнутый — с друп(м ш.)ходом запоминающего конденсатора и со входом компарятора, выход которого через логическое устройстго соединен с управляющим входом второго управляемого перекл)очателя.

48288с1

Составитель Н. h,",<ипсввв

Техред Т. Миронова 1i;оррскт<>0 E. Ровс<:i:ì

Редактор 11. Колида

Череиовецкав горочскаи т:и!огра

Закал 7940 Изд. № 1737 Тираж 902 11одписи<к

ЦНИИПИ Государственного ко»пггста Совета Мини тр«в СССР по тселам нлооретснии п Открыти

i!3035, Москва, 1(-35, Раугпская ис!