Делитель на 5

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii) 482899

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со:оз Советских

Сощиалистических

Республик (61 ) Дополните I!Hoe к авт. свид-13)! (22) 3 аявлено 25.08.72 (21) 1824223/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.08.75. Бюллетень № 32

Дата опубликования описания 17.10.75 (51) М. Кл. Н 03k 23 02

Государственный комитет

Совета Миниотров СССР (53) ДК 621.374.32 (088.8),go делам изобретений и открытий (72) Авторы изобретения В. А. Грехнев, М. Ф, Никеров, Ь. Л. Останков и H. П. Павлюченков (7l) Заявитель (54) ДЕЛИТЕЛЪ HA 5

Изобретение относится к области автоматики и вычислительной техники и предназначено для деления последовательности входных импульсов на 5.

Известен делитель на 5, содержащий 3 ячейки, каждая из которых состоит из логического элемента «И вЂ” НЕ», выход которого подключен к первому входу элемента памяти и коммутационного триггера, единичный вход которого соединен с выходом элемента памяти и с одним из входов логического элемента «И—

НЕ», единичный выход — с другим входом логического элемента «И вЂ” НЕ», а нулевой выход — с единичным входом элемента нам яти.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в первую ячейку введен вспомогательный логический элемент «И — НЕ», первый вход которого соединен с выходом логического элемента «И вЂ” НЕ», второй вход — с нулевым входом коммутационного триггера, со вторыми входами элементов памяти порвой и второй ячеек, а выход — с третьим и вторым входами элементов памяти второй и третьей ячеек соответственно, во вторую ячейку введены дополнительный элемент памяти, и вспомогательный логический элемент «И — НЕ», выход которого соединен со входом дополнительного элемента памяти, первый вход — с выходом логического элемента «И вЂ” HE», а второй вход — с выходом дополнительного элемента памяти, при этом четвертый вход элемента памяти второй ячейки соединен с единичным выходом коммутационного триггера третьей ячейки.

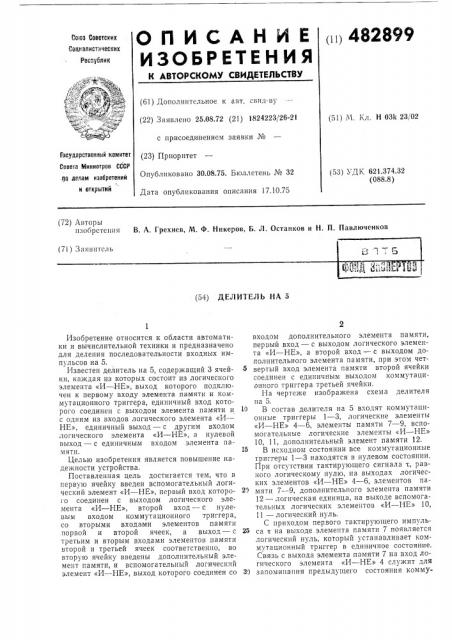

На чертеже изображена схема делителя

ыа 5.

В состав делителя на 5 входят коммутационные триггеры 1 — 3, логические элементы

«И — НЕ» 4 — 6, элементы памяти 7 — 9, вспомогательные логические элементы «И — НЕ»

10, 11, дополнительный элемент памяти 12.

В исходном состоянии все коммутационные триггеры 1 — 3 находятся в нулевом состоянии.

При отсутствии тактирующего сигнала т, равного логическому нулю, на выходах логических элементов «И вЂ” НЕ» 4 — 6, элементов памяти 7 — 9, дополнительного элемента памяти

12 — логическая единица, на выходе вспомогательных логических элементов «И вЂ” HE» 10, 11 — логический нуль.

С приходом первого тактирующего импуль25 са т на выходе элемента памяти 7 появляется логический нуль, который устанавливает коммутационный триггер в единичное состояние.

Связь с выхода элемента памяти 7 на вход логического элемента «И вЂ” НЕ» 4 служит для

30 запоминания предыдущего состояния комму482899

Составитель М. Аудринг

Техред 3. Тараненко

Корректор T. Фисенко

Редактор Н. Коляда

Подписное

Тираж 902

Изд. № !728

Заказ 2552717

Типография, пр. Сапунова, 2 тационного триггера 1 на время действия тактирующего сигнала. После окончания действия тактирующего сигнала на выходе логического элемента «И вЂ” НЕ» появляется логический нуль, а на выходе вспомогательного логического элемента «И вЂ” НЕ» 10 — логическая единица. Поэтому с приходом второго тактирующего сигнала логический нуль появляется па выходе элемента памяти 9, который устанавливает коммутационный триггер 3 в едп- 10 ничпое состояние, а коммутационный триггер

1 в нулевое состояние. Логический нуль на выходе элемента памяти 8 с приходом второго тактирующего сигнала не появится, так как на вход его поступает логический нуль с выхо- 15 да элемента памяти 9 раньше, чем изменение значения сигнала с единичного выхода коммутационного триггера 3. Поскольку логический нуль с выхода элемента памяти 9 поступает и на входы элементов памяти 7, 8, то на 2 их выходах логический нуль также не появится, хотя коммутационные триггеры 1 и 3 изменили свое состояние. После окончания действия второго тактирующего сигнала на выходе логического элемента «И вЂ” НЕ» 4 появляет- 25 ся логическая единица, а на выходе вспомогательного логического элемента «И вЂ” IE» 10— логический нуль, поэтому с приходом третьего тактирующего сигнала на выходе элемента памяти 7 появляется логический нуль, который 80 устанавливает коммутационный триггер 1 в единичное состояние. После окончания действия тактирующего сигнала па выходе логического элемента «И вЂ” НЕ» 4 — логический нуль, на выходе вспомогательного логическо- 85 го элемента «И вЂ” НЕ» 10 — логическая единица. С приходом четвертого тактирующего сигнала логический нуль появляется на выходе элемента памяти 8, который устанавливает коммутационный триггер 2 в единичное со- 4) стояние, логический нуль на выходе элемента памяти 9 не появится, так как на выходе логического элемента «И вЂ” НЕ» б — логический нуль. После окончания действия четвертого тактирующего сигнала на выходах испо l0faтельных логических элементов «И вЂ” IE» 10 и

11 будег логическая единица, а на выходах логических элементов «И вЂ” НЕ» 4, 5, б — логический цуль, поэтому с приходом пятого тактирующего импульса логический нуль появится па выходе дополнительного элемента памяти 12, который устанавливает коммутационные триггеры 1, 2, 3 в нулевое состояние и схема возвращается в исходное состояние.

Предмет изооретения

Делитель на 5, содержащий 3 ячейки, каждая из которых состоит из логического элемента И вЂ” HE, выход которого подключен к первому входу элемента памяти и коммутационного триггера, единичный вход которого соединен с выходом элемента памяти и с одним из входов логического элемента И вЂ” НЕ, единичный выход — с другим входом элемента

И вЂ” НЕ, а нулевой выход — с единичным входом элемента памяти, о т л и ч а ю щ н и с я тем, что, с целью повышения надежности, в первую ячейку введен вспомогательный логический элемент И†HE, первый вход которого соединен с выходом логического элемента

И вЂ” НЕ, второй вход — с нулевым входом коммутационного триггера, со вторыми входами элементов памяти первой и второй ячеек, а выход — с третьим и вторым входами элементов памяти второй и третьей ячеек соответственно, во вторую ячейку введены дополнительный элемент памяти и вспомогательный логический элемент И вЂ” НЕ, выход которого соединен со входом дополнительного элемента памяти, первый вход — с выходом логического элемента И вЂ” НЕ, а второй вход — с выходом дополнительного элемента памяти, при этом четвертый вход элемента памяти второй ячейки соединен с единичным выходом коммутационного триггера третьей ячейки.