Ячейка памяти

Иллюстрации

Показать всеРеферат

ио. ь - » биб

ОПИСАЙИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ i<) 4837lO

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 29.05.73 (21) 1923018/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 05.09.75. Бюллетень № 33

Дата опубликования описания 10.02.76 (51) М. Кл. G 1lc 11/40

Государственный комитет

Совета. Министров СССР ло делам изобретений и открытий (53) УДК 681.327(088.8) (72) Авторы изобретения

В, В. Баринов, В. Я. Контарев, О. Л. Крамаренко, В. И. Мошкин и А. А. Орликовский

Московский институт электронной техники (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области полупроводниковых интегральных схем памяти и Может быть использовано в оперативных ЗУ

ЦВМ среднего и высокого быстродействия.

Известны ячейки памяти, представляющие собой триггер с нагрузочными и развязывающими транзисторами, выполненными в структуре с совмещенными диффузионными областями, Такая ячейка памяти изготовляется в одном изолированном кармане в эпитаксиальной пленке п-типа со скрытым сильно легированным и+-слоем, расположенной на подложке р-типа проводимости. В эпитаксиальной пленке созданы базовые и инжектирующая области р-типа, причем каждая базовая область содержит по две коллекторные области. Скрытый п+-слой расположен под всей структурой и служит сильно легированным эмиттером n — р — п-транзисторов, которые в этом случае работают в инверсном режиме.

Низкая помехоустойчивость известной структуры обусловлена наличием больших паразитных токов в разрядных шинах.

Целью изобретения является разработка структуры ячейки памяти, совмещающей триггерные транзисторы с высокими инверсными коэффициентами усиления по току и развязывающие транзистор с низкими коэффициентами усиления. Это позволяет исключить паразитные токи и повысить помехоустойчивость.

Эта цель достигается за счет расположения сильно легированного скрытого слоя под инжектирующей областью и теми коллекторными областями, которые соединены с противоположными базовыми областями.

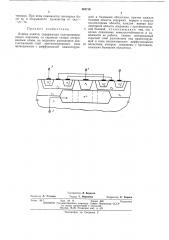

Структура ячейки памяти представлена на чертеже.

Ячейка содержит полупроводниковую подложку р, эпитаксиальный слой п1 со скрытым сильно легированным слоем и+, инжектпрующую область рь базовые области р2 и рз, коллекторные области п2,, п3, п;, п;, вывод инжек15 тора 1, шину адреса 2 и разрядные шины 3 и 4.

Ячейка памяти работает следующим образом.

В режиме хранения на шину 1 подается по2р ложительный потенциал, определяющий токовый режим работы схемы. Один из триггерных транзисторов n+(n ) — рз — n2 или

n+(n,) — рз — n, включен и насыщен, а другой (предположим, последний) выключен. При

25 считывании повышается потенциал на шине 1.

При этом с включенного плеча триггера (на шине 3) снимается сигнал, определяющий хранимую информацию. Для записи информации на шину 4 подается открывающий по483710

Предмет изобретения

Составитель В. Баринов

Техред Т. Миронова

Корректор О. Тюрина

Редактор Л. Утехина

Заказ 85/7 Изд. № 74 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

3 тенциал. При этом понижается потенциал базы рг, и открывается транзистор и+ (n )— — pa — пз

Ячейка памяти, содержащая полупроводниковую подложку со скрытым сильно легированным слоем, на подложке расположен эпитаксиальный слой противоположного типа проводимости с диффузионной инжектирующей и базовыми областями, причем каждая базовая область содержит первую и вторую коллекторные области, каждая первая коллекторная область соединена с противополож5 ной базовой, отличающаяся тем, что, с целью повышения помехоустойчивости и надежности ее работы, сильно легированный скрытый слой расположен под инжектирующей и теми коллекторными диффузионными

10 областями, которые соединены с противоположными базовыми областями.