Устройство для спектрального анализа

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii) 484528

ИЗОБРЕТЕН ИЯ, Савэ Сааетсиих

Сааналнсткчаснвх т ссау6.":нх (61) Дополшггельпое к clI3i . свид-ву (22) Заявлено 30.05.73 (21) 1923109/18-24 (51) N, Кл. 6 06@ 7/19

G 01г 23/00 с присоединением заявки «¹

Гссусгрстаеиьй нсэнтгСиэета т1нннст;1ад СССР па далвм нзобрстсинй н аткрытнй (23) Приоритет

Опубликовано 15.09,75. Бюллетень М 34

Дата опубликования описания 04.01.76 (53) УДК 681.333:519.2 (088.8) (72) Авторы изобретения

С. С. Березин, Е. Д. Колтик, Е. И. Коровкин, В. П. Пиастро и В. В. Сидоренко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА

Изобретение относится к области специализированных средств аналоговой вычислительной техники, предназначенной для спектрального анализа широкополосных детерминированных и случайных сигналов.

Известны устройства для спектрального анализа, содержащие генератор импульсов, подключенный через коммутатор к управляющим входам квантователей, входы которых соединены с входом устройства, а выходы— с соответствующими ячейками памяти. Такие устройства имеют низкое быстродейстие, обусловленное необходимостью выполнения большого числа арифметических операций, число которых пропорционально квадрату числа дискретных отсчетов.

В целях повышения быстродействия предлагаемое устройство содержит последовательно соединенные матрицы аналоговых вычислительных ячеек, причем входы аналоговых вычислительных ячеек первой матрицы подключены к выходам соответствующих ячеек памяти.

Аналоговая вычислительная ячейка содержит два инвертора и два суммирующих усилителя, причем один из входов ячейки подключен к первому инвертору и к одному из входов первого суммирующего усилителя, другой ее вход соединен с вторым инвертором, с другим входом первого суммирующего усилителя и с одним из входов второго суммирующего усилителя, другой вход которого подключен к выходу первого инвертора.

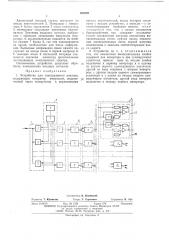

На чертеже показана блок-схема предла5 гаемого устройства.

Устройство содержит блок 1 преобразования входной информации, содержащий квантователи 2 по времени, блок управления 3 с генератором импульсов 4 и коммутатором 5, 1о блок 6, содержащий ячейки памяти 7, матрицы 8, состоящие из аналоговых вычислительных ячеек 9.

Сигнальные входы;всех временных кванто15 вателей 2 соединены параллельно, их управляющие входы связаны с выходами коммутатора

5, а выходы — с входами ячеек 7 памяти.

Выходы ячеек памяти подсоединены к входам аналоговых вычислительных ячеек 9, об20 разующих первую матрицу 8. Каждая ячейка 9 состоит из двух суммирующих усилителей 10 и двух инверторов 11, при этом входы инверторов и усилителей соединены с выходами ячеек памяти в соответствии с кон25 фигурацией дерева графа быстрого преобразования Фурье. Выходы ячеек 9 первой матрицы подссединены и определенным входам ячеек 9 второй матрицы (также в соответствии с конфигурацией дерева графа) и т. д, 30 Устройство работает следующим образом.

484528

Ол

1 и !

)|1

1-

)!! ! (! !!

1!! !!!!

gë, 1 ! — — <

Составитель В. новинский

Текред 3. Тараненко

Корректор Н. Аук

Редактор Т. Юрчикова

Заказ 3159/10 Изд. ¹ 1782 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Аналоговый входной сигнал поступает на входы квантователей 2. Импульсы с генератора 4 блока управления 3 через коммутатор

5 поочередно открывают временные квантователи. Значения входного сигнала, выбранные с периодом следования импульсов гене,ратора 4, последовательно подаются на ячейки памяти 7 блока 6, где они запоминаются на время, необходимое для ввода информации. Выходные напряжения ячеек памяти поступают на входы ячеек 9 первой матрицы 8.

С выходов ячеек 9 .последней матрицы сним аются значения амплитуд ортогональных составляющих комплексного спектра.

Описываемое устройство допускает обработку комплексных входных сигналов, Предмет изобретения

1. Устройство для спектрального анализа, содержащее генератор импульсов, подключенный через коммутатор к управляющим входам квантователей, входы которых соединены с входом устройства, а выходы — с соответствующими ячейками памяти, о т л и", а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит последовательно соединенные матрицы аналоговых вычислительных ячеек, причем входы аналоговых вычислительных ячеек первой матрицы подключены к выходам соответствующих яче1О ек памяти.

2. Устройство по п. 1, отличающееся тем, что аналоговая вычислительная ячейка содержит два инвертора и два суммирующих усилителя, причем один из входов ячейки

15 подключен к первому инвертору и к одному из входов первого суммирующего усилителя, другой ее вход соединен с вторым инвертором, с другим входом первого суммирующего усилителя и с одним из входов второго сум20 мирующего усилителя, другой вход которого подключен к выходу первого инвертора.