Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

» 484568

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.07.73 (21) 1944044/18-24 с присоединением заявки Ле— (23) Приоритет—

Опубликовано 15.09.75. Бюллетень Хе 34

Дата опубликования описания 05.04.76 (51) М.Кл. 6 11с 27/00

Гасударственный комитет

Совета Министров СССР аа делам иваоретений ч открытий (53) УДК 681.337(088.8) (72) Авторы изобретения

А. С. Ларионов и В. И. Гершов (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Предлагаемое изобретение относится к аналоговой вычислительной технике, точнее к области аналоговых запоминающих устройств, и может быть использовано в специализированных аналоговых вычислителях, контурах самонастройки с входной информацией в виде низкочастотных автоколебаний.

Известно запоминающее устройство, содержащее усилитель, накопитель, соединенный со входом усилителя, узлы заряда и разряда, входы которых соединены с выходом компаратора, а выходы их соединены со входом усилителя. Известны также модификации схемы данного запоминающего устройства. Основными достоинствами компараторных запоминающих устройств являются малый дрейф нулевого уровня и высокая точность при сравнительно простой и дешевой схеме усилителя, на вход которого подключен накопитель.

Однако у перечисленных ЗУ отсутствует ряд свойств, необходимых для применения их в контурах самонастройки. Одним из таких свойств является автоматический переход из режима запоминания в режим записи при

U„. ) U„,„., где U„напряжение на входе ЗУ; U„„. — напряжение на выходе ЗУ.

При этом постоянная времени записи ЗУ должна оыть неизменной и переходные процессы проходить с учетом начальных и конечных условий.

Вторым свойством является автоматический переход из режима хранения при

5 U,,- (U„,„.. При этом постоянная времени хранения должна быть неизменной, отличающейся на порядок от постоянной времени записи, переходной процесс должен проходить с учетом начальных и конечных усло1О в ий.

С целью повышения быстродействия предлагается аналоговое запоминающее устройство, которое содержит генератор опорного напряжения, два сумматора и дополнительный компаратор, выход которого соединен со входом узла заряда, положительный вход дополнительного компаратора соединен с выходом одного сумматора, а отрицательный вход — с выходом усилителя и с одним из входов другого сумматора, другой вход этого сумматора соединен с генератором опорного напряжения и с одним пз входов первого сумматора, другой вход второго сумматора подключен к входу устройства и к отрицательному входу компаратора, причем положительный вход этого компаратора соединен с выходом первого сумматора.

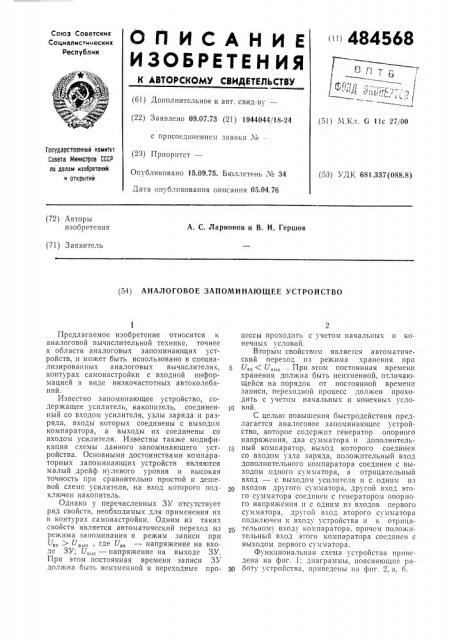

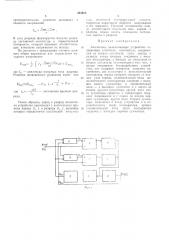

Функциональная схема устройства приведена на фпг. 1; диаграммы, поясняющие раЗ0 боту устройства, приведены на фиг. 2, а, б.

484568

В состав аналогового запомни",IOL его устройства, приведенного на фнг. 1> входят: iiaкопнтель 1, представля(ощий cni)n:.I ко! тенC3TOp C >)la ) l>I>II)r TOI(«3 )Ill у)счкн; > CII, I IITC. Ih 2 с входным сопротнв Ic)(((c» 10 о — -1О" Ом; у 3 c I 3 3 р Яд Я 8, )1 р сд с 1 «l 13 л 51 1011111 Й с О О О (i О 1(О—

СТЯОП II(3((PA IOLIQII)(;LB «. НО, IIOCIIIII(С 1(C) (0«!О)! на входе; узел разряда 4 — тnкocT;lбнлl1311рА lощнй двмхнолlосннк с к;почо)! III, 13>;n, Lc; генератор i) опорного нлнряжсI(ll:l, формнруlогцпи OTIIOIIOC(5(p)(hlc ОТрнцлТС i hi I hl il)(нульсы трсуголы)ой формы члстоты 1000 Гн, cI(ua>I()(0c(r>Io 10; 6, 7 — комнnр((т!)р! ), 8, !) сумматоры.

Ан«(логonoe 33110))l)III 3 In((Ice 1 cTPo(lcT(30 Р3ботаст следу)ощим образом.

Для случая У„х ) Уввх диаграммы, поясняющие работу схемы, приведены нл фнг. 2а. Сигнал с генератора 5 опорного напряжения суммируется с сигналом U,„,„. на сумматоре 8 и поступает на положительный вход компаратора 6, на отрицательный вход которого поступает сигнал U„, Как видно из диаграммы фнг. 2 я, напряжение на отрицательном входе компаратора 8 положительное н всегда больше амплитуды напря>кения У, В результате с выхода компаратора на управление ключом узла разряда ноступаст rrocT051LI(inc OTp)rl(aтсльнос напряжение lf ключ все время разори>л Т, ток с узла разряда не поступает Ilà няко)(итсль.

Сигнал U„, суммнруется с сигналом U„„на

c), )(млторс 9 ir c Hrixo,ra c) )(>)яторл 9

I I ÿc Il «! поло>кll тc,!(>н1>I) I 1)хn;I, 30. >! (I i р;> то!) л 7.

1 13 01 pII 1(3 TC l hH hi)(Вход I(n>)lllapHT() J) «I > )in сг>« I IHCò снГнял U„,„, . К«)к видно 113, (н «(Грл ммы, снГнял U>.>> мсньшс 3)I((.7НТ>, дь! снГпяла Ут„на величину, равную U„,.— U,,„. В результате на выходе компаратора 7 появляются положительные импульсы частоты

1000 Рц, длительность которых пропорциональна разности U„. U„„„, . Поло>кнтсльные импульсы, поступая на узел заряда, открывя!от ключ узла заряда. В рсзультятс на накопитель (конденсатор) начинают поступать импульсы тока постоянной амплитуды, длительность которых пропорциональна разности U„. — U„„, По мере заряда накопительной емкости разность U,, — U„,„óìåi(hшается. Прн U„,= U„,,„äëèòåëüíîñòü импульсов заряда становится равной нул)о, и процесс заряда прекращается. Для случая

U„,. (U„,„., как видно нз диаграмм, поясняющих работу схемы, сигнал U«>,... поступя)OIll,IIII )l3 0 (рицятс,(ын>)Й Iixo L I«:n«)III«lp«(TOJ)«l 7, всегда больше снгнл )3 1!5, посту:i;iiniilcr.

II «l нОЛО:к111 сгl!>1(hi)1 в О L hом(13 J) «I! О J) «I /. В рсзульглтс с выходя комнярлтора 7 л управление ключом уз.)3 aap>i;lя ндст постоянное 0Tp)ILL«lтсльIIoc н«l)!ряжснис i(е ilo«1 все

Вpc(>>15! p«lзомкliут. 1 Ок с ) Çля 3«lp51дя 1(c нО— ступ «I cT на на Ko)I IITC;II ы Й э. 1 см CIIT. С! (Гнал

U„, I(ocIóï3þùèé на OTp)lllaтглы)ый вх05( комплрятора 6, меньшс сш.нала U,, посту4 на)ощсго ня положительный вход компаратора 6 на величину, равну(о U„,,„— U„.

В результате с выхода комнаратора 6 на управление ключом узла разряда поступают положительные импульсы, длительность которых пропорциональная разности U„,,„. — U,, По мере разряда длительность положительны. импульсов с компаратора 6 уменьшастся. Прн U,,== U „„. длительность поло>киl0 тслы(ых импульсов с комнаратора 6 станет

Р 3 В НО !"1 Н >> Л 10.

Приведем основные соотношения, . арактсрнзующнс изменение напряжения на выходе устройства в зависимости от соотношения входного н выходного напря>кений. В зависимости от соотношения входного и выходного напряжений реализуются два режима работы.

1. Режим заряда реализуется при

U„.) UÄ,„, при этом компаратором 6 формируется длительность импульса, прямо пропорциональная разности входного и выходного напря>кений.

«>вх вых пз—

)в

«/

U — — f (l (>вх «>вых dI + U

40 вых 1 з

«> где С вЂ” величина интегрирующей емкости;

I, — амплитуда импульса тока заряда; Т— период опорного напряжения; U,„„— на45 пряжение на выходе устройства в момент переключения в режим заряда.

Решив приведенное линейное дифференциальное уравнение относительно U„,,„, получим

50 z

> «з + вых„ 7в = ((7в — оввз, ) 1 — е

ыСТ где 1з=, — постоянная времени заряда.

3,Цля упрощения получения конечного результата предполагается, что за время переходного процесса велич!ша входного напряжснii5i оставалась неизменной (реакция устpoIicT»;I па воздействие функции включеIII(5() .

2. Режим разряда реализуется прн

U„, (U„,„,, нри этом компаратором 6 фор05 мируется длительность импульса, прямо где lг — скорость изменения опорного напряжения.

После узла заряда формируется импульс тока постоянной амплитуды длительностью положительной полярности, поступающий в накопитель, выполняющий функции интегратора, напряжение с накопителя через

35- усилитель поступает на выход устройства.

11л ря>кение ня выходе устройства в этом случ Ie описывается выражением

484568

U»» — U„„„ вр к где ряда.

Вх

Ур нропорциональна51 разности выxoäíoãо и входного напряжений

В узле разряда формируется импульс разряда постоянной амплитуды и отрицательной полярности, который вызывает соответствующее изменение напряжения на выходе.

По аналогии с предыдущим случаем запишем общее выражение для определения выходного напряжения

С,. кТ вых„, где Ið — амплитуда импульса тока разряда.

Решение приведенного уравнения имеет вид

t вых (выхв вх ) Е р

<СТ постоянная времени раз1р

Таким образом, заряд и разряд накопителя устройства происходит с постоянными времени заряда (t, ) и разряда (t„), величина которых определяется амплитудо11 импульса тока, величггной иитегриру:ощсй емкости. скоростью нар аст IIII!5! опорного напряжения и его периодом. Пзменяя соотношение между амплитудами импульсов тока заряда и разряда, можно менять oTIIolllc!!èå постоя))lI1>Ix заряда и разряда.

Предмет изооретения

10 Аналогог>ое запоминающее устройство содер>кащее усилитель, накопитель, соединенный со входом усилителя, узлы заряда и разряда, входы которых îåäèíåíû с выходом комнаратора, а выходы их соедшгены со

13 входом усилителя, от.ггг гаюгггеегя тем, что, с целью повышения быстродействия устройства, оно содержит генератор опорного напряжения, два сумматора и дополнительный компаратор, выход которого соединен со Вхо20 дом узла заряда, положительный вход дополнительного компаратора соедгшен с Bhlxoдом одного сумматора, а отрицательньш вход — с выходом усилителя и с одним из входов другого сумматора, другой вход это25 го сумматора соединен с генератором опорного напряжения и с одним из входов первого сумматора, другой вход второго сумматора подключен к входу устройства и к отрицательному входу комнаратора, причем

30 положительный вход этого комнаратора соединен с В1>!кодо>>1 первого с >1>>1атора, 484568

Llb III

Риг 2

Редактор Б. Нанкина

Корректор Н. Стельмах

Заказ № 8233 Изд. ¹ 1812 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР

flo делам изобретений и открытий

113035, Москва, Ж-35, Раугпская наб., д. 415

МОТ, Загорский филиал о

Uon о о

Ь ь о îï о

У 1 и

Uir о

Составитель А. Воронин

Тсхрсд М. Семенов