Импульсно-временной дискриминатор

Иллюстрации

Показать всеРеферат

м1бл и

О п И С А Н И Е пц 48463I

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 07.01.74 (21) 1988241/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 15.09.75. Бюллетень № 34

Дата опубликования описания 5.1.76 (51) М, Кл. Н 03k 5, 20

Государственный комитет

Совета Министров СССР до делам изобретений и открытий (53) УДК 621.374,387 (088.8) (72) Авторы изобретения

С. И. Москаленко, М. И. Колесниченко, В. Е. Ткачук, А. А. Кузьмов и А. М. Котляр (71) Заявитель (54) ИМПУЛЬСНО-ВРЕМЕННОЙ ДИСКРИМИНАТОР

Изобретение относится к радиоэлектронике и может быть использовано в схемах стабилизации временного положения импульсов радиолокационных систем.

Известные импульсно-временные дискриминаторы, содержащие два триггера, на входах и выходах которых включены схемы «И — НЕ» и инверторы, и вырабатывающие сигналы, пропорциональные по длительности запаздыванию одного импульса относительно другого, имеют значительные погрешности и требуют наличия импульса сброса в цепи управления.

Для упрощения и повышения точности работы предлагаемого дискриминатора в него введена трехвходовая схема «И вЂ” НЕ», один вход которой соединен с выходом первой схемы «И — НЕ» и с входом инвертора, выход которого через .второй инвертор соединен с низкопотенциальным входом первого триггера, второй вход — с выходом другой схемы «И—

НЕ» и с входом третьего инвертора, выход которого через четвертый инвертор соединен с низкопотенциальным выходом второго триггера, вход которого соединен с входом первого триггера и выходом трехвходовой схемы

«И — НЕ», а ее третий вход подключен к входам первой и второй схем «И вЂ” HE» и выходу третьей схемы «И — НЕ», выходы которой подключены к другим входам первой и второй схем «И вЂ” НЕ».

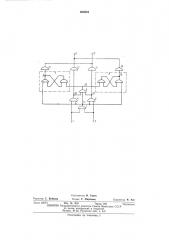

На чертеже представлена схема описываемого дискриминатора.

Известно, что если уровни «1» присутствуют на всех входах схемы «И — НЕ». то на ее выходы будет уровень «О». Урогснь «1» на выходе такой схемы будет в том случае, ссли хотя бы один из входных сигналов пмест уро10 вень «О».

В статическом состоянии (отсутствие входных сигналов на клеммах 1 и 2) на выходс схемы «И — НЕ» 3 будет уровень «1», на вы15 ходах схем «И вЂ” HE» 4 и «И вЂ” НЕ» 5 — также уровень «1», а на выходе схемы «И — НЕ»

6 — уровень сигнала «О». Триггеры 7 и 8 находятся в таком положении, что в точках 9 и

10 будут уровни «О», а, следовательно, на вы20 ходных клеммах дискриминаторов 11 и 12 сигналы отсутствуют (уровень «О»), так как на выходах инверторов 13 и 14 присутствуют уровни, сигнала «О» и они шунтируют сигналы «1» на выходах инверторов 15 и 16, Усло25 вием наличия сигнала на любом из выходов дискриминатора является наличие уровней

«1» на выходах обоих инверторов 13, 16, либо — 14, 15.

Дискриминатор работает следующим обра3о зом.

484631

При подаче импульса напряжения на клемму 1, на выходе схемы «И — НЕ» 3 сохранится уровень сигнала «1» (точка l i), на выходе схемы «И — НЕ» 4 — уровень сигнала «О» (точка 18), а на выходе схемы «И — НЕ» 5— уровень сигнала «1» (точка 19). На выходе схемы «И — HE» б появится уровень «1» (точка 20), при этом триггеры 7 и 8 не опрокидываются, так как по второму входу (точка 17) сохранится уровень «1». На вход инвертора

13 подается низкий уровень «О», а на его выходе и на выходе инвертора 16 будут уровни

«l», в результате чего на выходнои клемме дискриминатор а 11 появится уровень «1». 1 акое состояние сохранится до прихода импульса на входную клемму 2, при подаче которого потенциал на выходе схемы «И — НЕ»

3 (точка 17) изменится с уровня «1» на уровень «О», что приведет к опрокидыванию триггеров 7 и 8 в противоположные состояния. Одновременно в точке 18 появится уровень «i», а на выходной клемме дискриминатора 11 через инвертор 13 снова появится уровень «О». В точке 20 сохранится прежний уровень «1». llo окончании действия первого импульса в точке 17 появится уровень «1», при этом триггеры 7 и 8 останутся в прежнем положении, так как сохраняются уровни «1» в точках 18 и 20. В точке 19 появится уровень «О», что вызовет появление уровня «1» на выходе инвертора 14, но при этом на выходе инвертора 15 будет уровень «О» (триггер 7 опрокинут, в точке 9 уровень «1») и на клемме дискриминатора 12 устройства импульс не появится, Г1о окончании действия второго импульса выход схемы «И — НЕ» 3 имеет уровень «1», уровень сигнала в точках

18 и 19 — также «1», а уровень сигнала в точке 20 станет «О», в результате чего триггеры 7 и 8 опрокинутся и схема возвратится в исходное состояние.

Аналогично, в соответствующем порядке, устройство будет работать при подаче первого импульса на клемму 2. 1 аким образом, на обоих выходах дискриминаторов 11 и 12 в конкретных ситуациях выделяется импульс, длительность которого Определяется Временным положением передних фронтов входных импульсов.

При подаче обоих импульсов одновременно на обе входные клеммы 1 и 2, выход схемы

«И — НЕ» 3 изменится на «О», а в точках 18 и 19 сохранятся прежние уровни «1». В точке

20 появится уровень «1», и триггеры 7 и 8 опрокинутся. Инверторы 13, 14, 15, 16 на выходах имеют низкие уровни, а на выходных клеммах дискриминаторов 11 и 12 импульсы

5 не появятся. 11ри поступлении на входные клеммы 1 и 2 различных по длительности импульсов благодаря тому, что триггеры 7 и 8 опрокинуты уровнями «1» в точках 17 и 20, и сохранен уровень «1» в точке 20 по оконча1О нии действия более короткого импульса, на выходных клеммах дискриминаторов 11 и 12 устройства также не появятся импульсы, так как они зашунтированы открытыми инверторами 15 и 1б. и Дискриминатор работает с перекрывающимися по длительности импульсами, что характерно для систем взаимнои стабилизации временного положения двух импульсов при воздействии различных дестабилизирующих фак20 торов (температура, давление и т. д.). Гак как при передаче сигнала со входа устройства на его выход участвуют только три схемы «И — HE», то он имеет достаточное быстродействие. Мала ошибка импульсно25 временного дискриминатора и при пропуске импульса по одному из его входов. На выходе в таком случае выделится только длительность поступившего импульса.

30 Предмет изобретения

Импульсно-временной дискриминатор, содержащий два триггера, на входах и выходах которых включены схемы «И — НЕ» и инверторы, отличающийся тем, что, с целью упрощения и повышения точности работы устройства, в него введена трехвходовая схема «И вЂ” HE», один вход которой соединен с выходом первой схемы «И — НЕ» и с входом инвертора, выход которого через второй инвертор соединен с низкопотенциальным входом первого триггера, второй вход — с выходом другой схемы «И — HE» и с входом третьего инвертора, выход которого через чет4; вертый инвертор соединен с низкопотенциальным выходом второго триггера, вход которого соединен с входом первого триггера и выходом трехвходовой схемы «И — НЕ», а ее третий вход подключен к входам первой и

5О второй схем «И вЂ” НЕ» и к выходу третьей схемы «И — НЕ», выходы которой подключены к другим входам первой и второй схем «И—

НЕ».

484631

1

Составитель И. Горин

Техред Т. Миронова

Редактор С. Байкова

Корректор Н. Аук

Типография, пр. Сапунова, 2

Заказ 3207/1 Изд. № 1835 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-35, Раушская наб., д. 4/5