Преобразователь кода в код с большим основанием

Иллюстрации

Показать всеРеферат

(и) 4854 И

Своз Советских

Социалистических еаесяубпик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 02.07.73 (21) 1937538/18-24 с присоединением заявки № (51) М. Кл.

С 06 t 5/02

Гасударственный номитет

Совета Министров СССР па делам ивааретений н открытий (23) Приоритет—

/ (43) Опубликовано 25.09.75 Бюллетень № 85 (53) УДК681.з25.53 (088.8) (45) Дата опубликования описания 19.О2.76 (72) Авторы изобретения О. В. Викторов, В. А. Остафин, А. М. Романкевпч и А. И, Яцунов (7l) Заявитель Киевский ордена Ленина политехнический институт им. 50-летпя

Великой Октябрьской социалистической революции

Ф (54) ПРЕОБРАЗОВАТЕЛЬ КОДА В КОД С БОЛЬШИМ

ОСНОВАНИЕМ

Изобретение относится к вычислительной технике и автоматике и предназначено для преобразования кодов.

Известен преобразователь кода в код с большим основанием, содержащий схему алгебраического суммирования и предназначенный для преобразования двоичного кода в код с любым другим основанием, схему умножения на константу, схему управления.

Схемы алгебраического суммирования выполнены в виде релейно-диодных суммато- ров, число которых равно разрядности десятичного числа.

Недостатками известного преобразователя являются большая сложность сумматоров и ограни ченные функциональные возможности преобразователя.

Цель изобретения — упрощение преобразователя и расширение области его применения.

Для этого в предлагаемом устройстве схема алгебраического суммирования выполнена в виде двухразрядного вычитателя, выходы первого и второго разрядов которого соединены через соответствующие вентили с входами первого и второго старших рызрядов сдвигового регистра, выход первого старшего разряда этого регистры с:оединен с входами схемы умножения ны коп-. станту, первого разряда вычитателя и младшего разряда сдвигового регнс гры, с ! выхОдом второго старшего разряды котo()ol о

1 соединен вход второго разряда вычптытсиш.

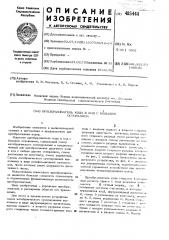

На фиг. 1 изображена блок-схемы прод—

fp лагаемого устройства; на фиг. 2 — диыг(пи мы управляющих сигналов, вырабсггьпыс:r,iû» схемой управления устройством при преооразовании четырехразрядных кодов.

И Преобразователь кода содержит k-разряд ный регистр сдвиги 1 (под разрядом псигнмается Я -ичный разряд„ i до

1 основание системы счисления, в которусо переводится код), двухрызрядный вычитсгсоль

20 2, схему 3 умножения на константу, воп1или 4, 5, схему управления 6. Выход ст ив щего разряда 7 регистры 1 соединен с их—

I дом младшего разряда того же роrис гJ> s, также с входом умеиьшаемо о разряды 8

25 вычитателя 2 и входом схемы 3. Выход

4/5444 другого старшего разряда 9 регистра подключен к входу уменьшаемого разряда 10 вычитателя 2. Вход вычитаемого разряда 8 вычитателя 2 объединен с выходом перено- сов 11 схемы умножения 3, а вход вычитаемого разряда 10 вычитателя 2 соединен с выходом результата 12 схемы 3. Выход разряда 8 вычитателя 2 через вентиль 4 подключен к входу разряда 7 регистра 1, а выход разряда 10 через вентиль 5 - к входу разряда 8 регистра. Схема управления 6 подает управляющие сигналы на регистр и вентили 4, 5 по шинам 13, 14.

Все схемы, входящие в состав устрой ства, предназначены для работы с кодами чисел в системе счисления с тем основанием, с которым необходимо получить результат; k-разрядный код целого числа, которое необходимо преобразовать, помешают в регистр 1. Старший разряд кода числа регистра поступает па схему 3, где происходит умножение его на константу, равную разности оснований систем счислейий. На вычитателе 2 из двух старших разрядов кода числа, поступающих из perèñòðà 1, вычитается код числа, поступаю ций из схемы 3. На вентили 4 и 5 из схемы 6 по шине 14 поступает разрешиоший сигнал, в результате чего полученная разность записывается в регистр. Под действием следующего управляющего сигнала, поступающего из схемы управления 6 в регистр 1, происходит сдвиг содержимого регистра на один разряд (от младших разрядов к старшим); при этом код, хранящийся в старшем разряде 7 регистра 1, переписывается в младший разряд. На (ц (k-1)+ $) = ом такте в регистре получаем код числа с новым основанием.

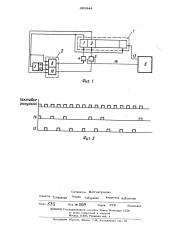

За первые 2к тактов на шину 13 (см. фиг. 2) поступает последовательность из

k-1 сигналов, и в каждые последующие

2 ° х тактов она уменьшается на единицу.

За каждые 2 k тактов на шину 13 поступает последовательность из к сигналов, отстающая на такт от последовательности на шине 14.

Работу устройства можно проиллюстрировать на следующем примере:

5 (1507) =(X); (1507)

1ч 1 507

3

1207

847

3

12

838

24

59 (1 507) =45952

7 tQ

Предмет изобретения

25 !

Преобразователь кода в код с большим основанием, содержащий схему алгебраиче-; ского суммирования, схему умножения на константу, схему управления, выходы которой соединены со входами сдвигового регистра и вентилей, о т л и ч а ю ш и йс я тем, что, с целью упрощения устройства и расширения области его применения, схема алгебраического суммирования выполнена в виде двухразрядного вычитателя, выходы первого и второго разрядов которого соединены через соответствующие вентили с входами первого и второго старших разрядов сдвигового регистра, выход первого старшего разряда этого регистра соединен

40 с входами схемы умножения на константу, первого разряда вычитателя и младшего разряда сдвигового регистра, с выходом второго старшего разряда которого соединен

45 вход второго разряда вычитателя.

485444

Составитель В Игнатушенко нова Teõðeà ванова

Заказ З

Изд. hL 03

Тираж 679

Подписное

ЛилИые ачлулым

Т.Кури ко корректор A.дзеоова

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )13035, Раушская иаб., 4

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24