Устройство для деления чисел с восстановлением остатка

Иллюстрации

Показать всеРеферат

. л."н

I .о-" . :ничвокя9

-,, ото(К мЯ (») 485447

Союз Советских

Социалистииеских

Республик

ОП ИСАНИЕ

ИЗОВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 3 0.11,72 (21) 1854580/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано25.09.75 Бюллетень № д5 (51) Ы. Кл. (06 t" 7/39

Государственный комитет

Соната Министров СССР по делам изооретоннй и открытий (1@) УД1 681.325.б (088.8) (45) Дата опубликования описания 19 02 76 (72) Авторы изобретения

Ф. Ф. Мингалеев и А. А. Князюк (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ С ВОССТАНОВЛЕНИЕМ

ОСТАТКА

Изобретение относится к вычислитель- ной технике и может быть использовано в арифметических устройствах.

Известно устройство для деления чисел с восстановлением остатка, содержащее регистр делителя, основной и вспомогательный регистры делимого и частного, сумматор, схему формирования цифр частного, и инвертор, причем шина тактовых импульсов устройства соединена с единич- !0 ным входом знакового разряда регистра делителя, с первым входом схемы формирования цифр частного и с входом инверто ра, выход которого подключен ко второму входу схемы формирования цифр частного, И с третьего по седьмой входы которой подключены соответственно к единичному и нулевому выходам знакового разряда регистра делителя, к нулевому выходу знакового разряда сумматора и к единичному 20 и нулевому выходам знакового разряда основного регистра делимого, а выход— к входу первого разряда регистра частного, при этом выходы разрядов регистра делите ля соединены с соответствующими первы- И ми входами сумматора, вторые входы которого в каждом разряде подключены соответственно к выходам основного регистра делимого и к первым входам схем "И", вторые входы которых соединены с шиной тактовых импульсов устройства.

Цель изобретения — увеличение быстродействия устройства.

Достигается это благодаря тому что в его состав введены первая и вторая дополнительные группы схем И", причем первые входы первой дополнительной группы схем

"И" соединены с соответствующими выходами разрядов сумматора, вторые входы— с нулевым выходом его знакового разряда, третьи входы — с первыми входами второй дополнительной группы схем И" и с выходом инвертора, а выходы — с соответствующими входами схем ИЛИ", выходы которых связаны соответственно с входами вспомогательного регистра делимого.

Вторые входы второй дополнительной группы схем "И соединены с единичным выхо— дом знакового разряда сумматора, третьи выходы — с соответствующими первыми

485447 4 входами схем "И", выходы которых подключены соответственно ко вторым входам схем "ИЛИ", третьи входы которых соединены с соответствующими выходами второй дополнительной группы схем "И". Это позволяет ускорить операцию деления, На чертеже приведена схема предлагаемого устройства.

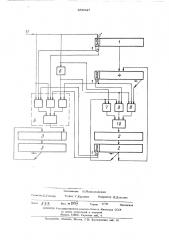

Устройство для деления чисел с восстановлением остатка состоит из регистра 1 10 делителя, основного и вспомогательного регистров 2 делимого, основного и вспомогательного регистров 3 частного, сумматора

4, схемы 5 формирования цифр частного, инвертора 6, схем "И" 7, первой дополни- 15 тельной группы 8 схем "И", второй дополнительной группы 9 схем "И, схем "ИЛИ"

10 и шины 11 тактовых импульсов.

В режимах делимого и частного выходы вспомогательных регистров соединены с 20 входами основных регистров параллельными цепями, а выходы основных регистров— с входами вспомогательных регистров цепями сдвига на один разряд влево. Сдвиг содержимого регистров 2 и 3 производится двумя тактируюшими имггульсмли внутри такта.

Шина 1 1 тактовых импульсов соединена с едиии шым входом знакового разряда регистра делителя 1, с первым входом схемы формирования цифр частного и с входом инвертора 6, выход которого подключен ко второ»у входу схемы формирования цифр частного с третьего по седьмой входы которой т

35 подключены соответственно к единичному и нулевому выходу знакового разряда регистра делителя 1, к нулевому выходу знакового разряда сумматора 4 и к единичному и нулевому выходу знакового разряда

40 основного регистра делимого 2, а выход— к входу первого разряда регистра 3 частного, при этом выходы разрядов регистра делителя l соединены с соответствуюшими первыми входами сумматора 4, вторые

45 входы которых в каждом разряде подключены соответственно к выходам основного регистра 2 делимого и к первым входам схем "И" 7, вторые входы которых соединены с шиной 11 тактовых импульсов.

Первые входы первой дополнительной груипы 8 схем "И соединены с соответствующими выходами разрядов сумматора

4, вторые входы — с нулевым выходом его знак свого разряда, третьи входы — с первыми входами второй дополнительной группы 9 r хем "И" и с выходом иивертора 6, а выходу — с соответствующими первыми входами схем "ИЛИ" 10, выходы которых свя;игны соот ветственно с входами вспомо1

l гательного регистра делимого 2, вторые входы которой дополнительной группы схем

"И" - с единичным выходом знакового разряда сумматора 4, третьи входы — с соответствующими первыми входами схем

"И" 7, выходы которых подключены соответственно ко вторым входам схем «ИЛИ»

10, третьи входы которых соединены с соответствуюшими выходами второй дополнительной группы 9 схем И .

Схемы "И-ИЛИ" совмещаются с входными логиками триггеров вспомогательных регистров 2 и 3.

Прямое и обратное значения знакового ! разряда сумматора 4 формируются одновремен но.

Работа устройства происходит следующим образом, При делении двух чисел, заданных прямым кодом, код делимого направляется на регистр 2 в прямом коде, а код- делителя — на регистр 1 в дополнительном коде, так как в сумматоре 4 производится только вычитание делимого (остатка) и делителя.

По сигналу первого такта по шине 11 определяется знак частного. При совпадении знаков делимого и делителя (00 или

11) в младший разряд регистра частного 3 записывается "1 ". В конце первого такта в регистре 2 производится сдвиг делимого на один разряд влево, а в знаковый разряд регистра делителя 1 записывается

А 1 Ф

Таким образом, деление двух чисел с произвольным сочетанием знаков сводится к делению двух положительных чисел.

В начале второго такта содержимое регистров 2 и 3 из вспомогательного регисг ра параллельно записывается в основной регистр.

В конце второго такта анализируется знак кода остатка на выходе сумматора 4.

Если в знаковом разряде сум м а тора 4 оказывается 0", то в младший разряд регистра 3 частного записывается "1„" а код остатка с сумматора 4 по цепям сдвига на один разряд влево записывается на регистр 2. Если в знаковом разряде сумматора 4 оказывается "1", то в младший разряд регистра 3 частного записи не производится и в нем сохраняется нуль, а в регистре 2 производится сдвиг содержимого на один разряд влево (восстановление остатка).

В регистре частное передается из основного регистра на вспомогательный со сдвигом на один разряд. влево.

@f5447

В начале следующего такта на регистре 2 находится код остатка, сдвинутый на

; один разряд влево. Работа устройства для, деления чисел происходит аналогично предыдущему такту, 6

Предмет изобретения

Устройство для деления чисел с восста новлением остатка, содержащее регистр де- 10 лителя, основной и вспомогательный регистры делимого и частного, сумматор, схему формирсаания цифр частного и инвертор, причем шина тактовых импульсов устройства соединена с единичным входом знако- 15 вого разряда регистра делителя, с первым входом схемы формирования цифр частного и с входом инвертора, выход которого подключен к второму входу схемы формирова« ния цифр частного, входы которой с третье- 20 го по седьмой подключены соответственно, к единичному и нулевому выходам знаковоI го разряда регистра делителя, к нулевому выходу знаковоголразряда сумматора и к единичному и нулевому выходам знакового разряда основного регистра делимого, а выход - ко входу первого разряда регистра частного, при этом выходы разрядов регистра делителя соединены с соответствую1

30 шими первыми входами сумматора, вторые входы которого в каждом разряде подключены соответственно к выходам основного регистра делимого и к первым входам схем

И, вторые входы которых соединены с шиной тактовых импульсов устройства, т отличающееся тем, что,с целью увеиичения быстродействия, в состав устройства введены первая и вторая дополнительные группы схем И", причем первые входы первой дополнительной группы соединены с соответствующими выходами разрядов сумматора, вторые .входы — с нулевым выходом его знакового разряда, третьи входы — с первыми входами второй дополнительной группы схем "И" и с выходом инвертора, а выходы — с соответствующи ми первыми входами схем "ИЛИ", выходы которых связаны соответственно со входами вспомогательного регистра делимого, вторые входы второй дополнительной группы схем И вЂ” с единичным выходом знакового разряда сумматора, третьи выходы— с соответствующими первыми входами схем

И", выходи которых подключены соответственно ко вторым входам схем ИЛИ", третьи входы которых соединены с соответствующими выходами второй допогпш-, тельной группы схем "И", 485447

Составитель 11 Ìèëîñëàâcêàÿ

Редактор Е„Гончар

Техред Т.Курилко

Корректор Л.Дзесова и., и lOb)

Тираж Подписное

Заказ

Предприятие «11атент», Москва, Г-59, Бережковская наб,, 24

ЦНИИГ1И Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, 113035, Раушская наб„4