Устройство для асинхронного уплотнения каналов связи с временным разделением сигналов

Иллюстрации

Показать всеРеферат

у„,к„, - "зсщави

ОПИСАНИЕ оц 4вв4ва

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

СОюз С4ввтскик

Социалистических о есаубв к (61) Дополнительное к авт. свид-ву(22) Заявлено 16.02.73 (21) 1884268/ 8-24 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 25 09 75 Бюллетень № 35 (51) М Кл С 08С 15/06

H 04 j 3/00

Государственный иаиитет

6аввтв Министров СССР во долам извбрвтввий и открытий (53) УДК 621.398 (088. 8) Дата опубликования описании 28.11.75) (72) Авторы изобретении

В. Ф. Зенкин, Г, П. Абугов и И. B. Мягков

Центральный научно-исследовательский институт связы (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОГО УПЛОТНЕНИЯ КАНАЛОВ

СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ СИГНАЛОВ

20

Устройство относится к электросвязи и может быть использовано в аппаратуре асинхронной передачи двоичной информации.

Среди высокоэффективных методов асинхронного ввода особый интерес представ. ляет метод стаффицга, при котором для передачи сигналов, позволяющих скорректировать фазовые сдвиги частоты сигнала относительно частоты представляемос го канапа связи t, используется дополн нительный канал, обычно составляющий часть передаваемого по линии связи потока.

Известно устройство асинхронного ввода двусторонним стаффингом с двумя командами управления j КУ) и отслеживанием текущих значений фазы входного сигнала относительно тактовых позиций канала связи; Для повышения достоверности приема КУ, зависящей от числа допустимых сбоев посылок, составляющих команду, не приводящим к нарушению, правильности

- приема этой команды, обычно используют о

3-15 символьные КУ. Увеличение числа символов в КУ ведет к снижению частоты их следования Г, что снижает точность ° к отслеживания фазы, или при неизменной точьости отслеживания - к уменьшению допусков на нестабильность частот f u

/,.

Цель изобретения — повышение помехоустойчивости устройства.

Достигается это тем, что в устройство введены на передающей станции - схема сдвига, пороговая схема, схема задержки и триггер, причем второй ход пороговой схемы подключен к первому выходу блока эластичной памяти, выход норр оврй схемы задержки — к входу блока изменения скорости считывания и к третьему входу схемы сдвига. Четвертый вход этой схемы через триггер подключен, к выходу формирователя команд, выход схемы сдвига подключен к входу фазового детектора, а на приемной станции введены дифференцирующая и интегрирующая схемы, триггер и схема сдвига, причем второй вход блока эластичной памяти через схему сдвига подключен к фазовому детектору, выход

4854.88 дешифратора команд соединен через триг- 1 гер с соответствующим входом схемы сдви1 га и через последоЬательно соединенные интегрирующую и дифференцирующую схемы подключен к входу блока изменения

1 скорости считывания.

Таким образом в предлагаемом устрой1 стве произведено разделение отслеживания л текущих значенйй фазовых сдвигов 1 и

И и компенсации этих сдвигов в эластичс ной памяти. При этом сбои отдельных команд не вызывают перерывов в связи, бла- годаря чему появляется возможность использования 1-3 символьных КУ, что приводит к увеличению / . Увеличение f к к позволяет увеличить допуски на нестабильность частот t и (или увеличить точи, с ность отслеживания.

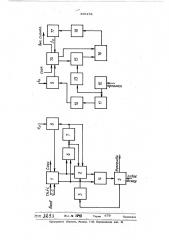

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит на передаче блок 1 эластичной памяти схему сдвига 2, триг- гер 3, фазовый детектор 4, формирователь команд 5, пороговую схему 6, схему задержки 7, блок изменения скорости считывания 8, а на приеме блок 9 изменения скорости записи, дифференцирующую схему

10, интегрируюшую схему 11, дешифратор команд 12, триггер 13, блок 14 эластичной памяти, схему сдвига 15, фазовый детектор 16, генератор 17 и фильтр 18 низких частот.

Поступающий на передающую станцию сигнал записывается в блок 1 эластичной памяти на тактовой частоте (. Считывас

we информации осуществляется частотой, f поступающей через блок изменения н скорости считывания одной из ячеек памяти, причем один из выходов блока эластичной памяти связан с входом фазового детектора 4. непосредственно,. а другбй— через схему сдвига 2.: Сигнал с выхода фазового детектора 4 поступает на формирователь команд 5, который на командных позициях дополнительного канала формирует одну из команд, зависящую от знака действующего напряжения на выходе фазового детектора 4. В случае, если .() ) О, то формируется команда фаз. дет.

А, если (/ (О, то формируется фаз. дет. команда Б. Выход формирователя команд связан с одним из входов схемы сдвига 2 о .чФрез триггер 3, пропускающим íà схему одвига после команды А, команду типа Б, If наоборот, после команды Б на схему сдвига могут поступать лишь команды типа ф. Последовательность команд, прошед- t ших на схему сдвига 2, такова, что усред ненный во времени фазовый сдвиг, вызванный этой последовательностью, близок к временной функции сдвига чаотот и н с

Сформированная последов ательность команд не вызывает изменений скорости считывания информации из блока эластичной памя. ти Компенсация расхождения частот осуществляется тем же способом, что и при

10 Ф обычном стаффинге без отслеживания. Ког да фазовый сдвиг частот 1 и 1 достин с

15 ции из блока эластичной памяти в этот мо20 мент не происходит, поскольку на прием45

35 гает одного тактового интервала частоты

f, срабатывает пороговая схема 6. Сиги нал с выхода этой схемы воздействует на схему сдвига 2, вызывая компенсацию этого сдвига на входе фазового детектора 4.

Изменения скорости считывания информа,ной станции этот момент времени может быть обнаружен после передачи 2-4 очередных команд. С этой целью к.выходу пороговой схемы 6 подключена схема задержки 7, в качестве которой может использоваться счетчик или сдвиговый регистр.

Сигнал с выхода схемы задержки 7 воздействует одновременно на блок изменения скорости считывания 8 и схему сдвига 2.

При этом фазовый сдвиг, вводимый схемой

2 после срабатывания пороговой схемы 6, компенсируется. Блоком изменения скорости считывания 8 производится либо добавление лишнего считывающего импульса, либо устранение одного считывающего импульса, в зависимости от знака расстройки частот и f . При этом, в первом случае н с информация, считанная лишним считывающим импульсом, передается по дополнительному каналу, а во втором случае передается; балластная посылка в основном канале.

На приемной станции принятый сигнал записывается в блок 14 эластичной памяти с частотой, поступающей из блока н

9 изменения скорости записи. Считывание информации производится с частотой, вырабатываемой генератором 17 и с управляемым сигналом с выхода фильтра 18 низких частот. На вход фильтра низких частот поступает сигнал с выхода фазового детектора 16, входы которого связаны с выходами блока эластичной памяти 14, на которых имеются импульсы записи и считывания одной из ячеек памяти. Один из входов фазового детектора 16 связан с выходом блока эластичной памяти непосред-. ственно, а другой — через схему сдвига 15.

485488 Дешифратор команд 12 в соответствии с . принимаемыми командами управляет работой схемы сдвига 15 через триггер 13, а также управляет работой блока 9 изменения скорости записи через последовательно соединенные интегрирующую 11 и дифференцируюшую 10 схемы.

Благодаря наличию триггера 13 только часть принятых команд вызывает воздействие на схему сдвига 15. Так, после воздействия команды А очередное воздействие может произвести лишь команда Б, и, наоборот, после команды Б очередное воздействие может оказать лишь команда A. При сдвиге фаз между и н с близких к 2 Т, последовательность переданных команд в предлагаемом устройстве имеет вид (... ++++ ...) или (...— ++++... ) в зависимости от знака действующей расстройки частот и н . Смена серий одноименных команд обнаруживается с помощью интегрируюшей

11 и дифференцируюшей 10 схем после поступления 2-4 одноименных команд, сменивших предшествуюшую серию проти. воположных команд. Появляющиеся в эти .

1 моменты времени сигналы на выходе дифференцирующей схемы 10 воздействуют на блок изменения скорости записи, вызы- вая компенсацию фазовых сдвигов, равных тактовому и нтервалу частоты н . Поскольку в устройстве передаваемые команды не производят непосредственного воздействия на блок эластичной памяти, а управляют лишь работой генератора приемной станции, выделяющего тактовую частоту передаваемого сигнала, сбои отдельных команд вызывают лишь незначительное увеличение фазовых флуктуаций частоты Р на приемной станции, Неточность с в определении сверхцикла, в котором на передающей станции было произведено из1 меднение скорости считывания информации из блока эластичной памяти, приводит к перерыву в связи в один-два сверхцикла.

При этом абонентские устройства цикловой синхронизации не теряют состояния синхронизма. В связи с этим помехозащищенность команд может быть невысокой, т. е. использовать 1-3 символьные команды. Наибольшую частоту f можно полу к чить при положительном стаффинге, где выравнивание частот f и f осушосгьля.-, н ется за счет передачи балластных посылок в основном канале и не требуется огдельной позиции в дополнительном канале.

Предмет изобретения

Устройство для асинхронного уплотне, ния каналов связи с временным разделением сигналов, содержащее на передающей станции блок эластичной памяти, один

15 из входов которого подключМж блоку изменения скорости считывания, первый выход блока эластичной памяти через фазовый детектор подключен к одному из входов формирователя команд, а на приемной ъ0 станции — блок эластичной памяти, один вход которого соединен с выходом блока изменения скорости записи, а один из вы ходов через последовательно соединенные фазовый детектор.и фильтр низких частот р5 подключен..к входу генератора, выход которого соединен с вторым входом блока эластичной памяти, и дешифратор команд, 1 о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости устройства, в него на цередаюшей станции введены схема сдвига, пороговая схема, схема задержки и триггер, причем второй выход блока эластичной памяти подключен к первым входам пороговой схемы и схемы сдвига, второй вход пороговой схемы подключен к первому выходу блока эластичной памяти, выход пороговой схемы подключен ко второму входу схемы сдвига и через схемы задержки — к входу бло4р ка изменения cKopoctH считывания и к третьему входу схемы сдвига, четвертый вход которой через триггер подключен к выходу формирователя команд, выход схемы сдвига подключен к входу фазового

45 детектора, а на приемной станции введены дифференцирующая и интегрирующая схемы, триггер и схема сдвига, причем второй вход блока эластичной памяти через схему сдвига подключен к фазоиому

50 детектору, выход дешифратора команд соединен через триггер с соответствующим входом схемы сдвига и через последовательно соединенные интегрирующую и дифференцируюшую схемы подключен к входу блока изменения ск ор ости считыва ни я.

485488

ФОЭ

Изд. Ж !ф® Тираж

Заказ ЯЯ (Я

Подписное

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24 ИЧ о у