Устройство для сжатия двумерной информации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЙТЕЛЬСТВУ (61)Дополнительное к авт. свид-ву « (22) Заявлено 11.07.74(21) 2043300/18-24 с присоединением заявки ¹ (1ц 485489

Савз Советских

С©цианнстицескнх респубве (5}) М. Кл.

G 08с 19/28

Гасу,аврственаий наннтет

@вета Межтрав СКР в делам нзобретвннй и ютнритнй (23) Приоритет—

° Опубликовано 25 09.75,Бюллетень 36 35

Дата опубликования описания 28.11.75 (53) УДК 621.398 (088. 8) (») Авторы изобретения

B. А..Свириденко и В. В. Малеженков (71) Заявитель.Московский ордена Трудового Красного Знамени электротехнический институт связи (54) УСТРОЙСТВО ДЛЯ СЖАТИЯ ДВУМЕРНОИ ИНФОРМАЦИИ

Изобретение касается передачи данных,в частности передачи многоканальных аналоговых или аналого-дискретных телеметрируемых процессов или фото- и телевизионных изображений в цифровой форме, и может быть использовано в системах передачи массивов телеметрической информации и записи ее в цифровое запоминающее устройство.

Известно устройство для сжатия дву мерной информации, содержащее источник информации, выходы которого через дискретизатор подключены ко входу аналогоцифрового преобразователя, синхронизатор, подключенный к дискретизатору и первому входу сумматора, выход которого соединен с буферным запоминающим блоком.

Известное устройство не позволяет контролировать максимальную ошибку восстановления исходного сообщения, требует посылки в канал связи в каждый такт передачи фиксированного числа двоичных единиц и ограничено использованием только предсказателя на основе усреднения со: седних с предсказываемым элементом.

Цель изобретения - повысить надеж- . ность работы устройства и расширить его функпиональные возможности.

Для этого в него введены блоки апертурного сокращения избыточности но строкам и по столбцам, элемент запрета, управляющий элемент и генератор адресной информации, прячем выход аналого-цифрового преобразователя подключен соответственно через элемент запрета ко второму входу сумматора и через блоки апертурного сокращения избыточности по строкам и по столбцам ко входам управ ляющего элемента и генератора адресной

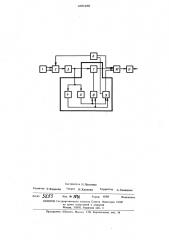

1к информации, выход управляющего элемента соединен со вторым входом элемента запрета, а выходы генератора адресной информации подключены к синхронизато« ру и третьему входу сумматора. рй На чертеже дана блок-схема предлагаемого устройства.

Устройство содержит источник информации; 1, дискретизатор 2, аналого-циф. ровой преобразователь (АЦП) 3, блок 4 р5. апертурного сокращения избыточности по

485489 строкам, блок 5 апертурного сокращения — избыточности по столбцам, синхронизатор, 6, элемент запрета 7, управляющий элемент 8, генератор адресной информации9, сумматор 10 и буферный запоминающий блок 11.

Устройство работает следующим образом.

Двумерный массив информации, представленный ЯИ-размерной матрицей (Я число строк, М вЂ” число столбцов), посту-

10 пает с выходов источника информации 1 на дискретизатор 2 и далее на АЦП 3.

Двоичная информация с выхода АЦП 3 поступает одновременно на элемент запрета

15 ! 7 и на блоки 4 и 5 апертурного сокращения избыточности. Блоки 4. и 5 могут реализовать любые алгоритмы сжатия данных предсказывающего и интерполирующего типа, в частности апертурные интер20 поляторы и предсказатели, контролирующие максимальную погрешность восстановления исходного сообщения, или ортогональные преобразователи, контролирующие квадратическую погрешность. Результаты анали25 за блоками сокращения избыточности 4 и 5 (существенна или несущественна данная выборка по строке или столбцу) поступают одновременно на управляющий элемент !

8 и генератор адресной информации 9.

Управляющий элемент 8 в зависимости ат результата анализа управляет элементом запрета 7, который либо пропускает двоичную информацию с выхода аналогоцифрового преобразователя на сумматор

10, либо нет.

Генератор адресной информации 9 формирует кодовые комбинации, содержащие информацию о местоположении как существенных, так и избыточных выборок по стро- 0 ке и столбцу исходной матрицы, представляющую входное двумерное сообщение, Временная синхронизация работы блока 9 осуществляется синхронизатором 6.

I В сумматоре 10 сигнал КИМ (уже 4 не содержащий избыточных выборок) суммируется с синхроссылкой и адресной информацией. Сформйрованный таким образом сигнал поступает далее в буферный запоминающий блок 11.

Работа приемного устройства, восста11авливаюшего по сжатым данным служеб4 ! ной (адресной) информации и синхропосылкам, переданным по синхронному каналу без помех, исходное двумерное сообщение, обратна работе устройства обработки двумерногю массива данных.

Адресация производится следующим oF>разом. Если выборка существеннее по столбцу и строке, то она кодируется двумя двоичными единицами "11", если только по столбцу, то "10". Если она избыточна по столбцу, то не зависимо от того, информативна она по строке или нет, соответствующая ей адресная комбинация состоит из одного нуля. В:последнем случае

I выборка восстанавливается всегда по столбцу. Адресную информацию в силу присущей ей избыточности можно далее статистически кодировать для сокращения этой избыточности (например, кодирование длин серий одинаковых символов), Предмет изобретения

Устройство для сжатия двумерной информации, содержащее источник информации, выходы которого через дискретизатор подключены ко входу аналого-цифро I вого преобразователя, синхронизатор, подключенный к дискретизатору и первому входу сумматора, выход которого соединен с буферным запоминающим блоком, отличающееся тем,что,с целью повышения надежности работы и расширения функциональных возм ожностей устройства, в него введены блоки апертурного сокрашения избыточности по строкам и столбцам, элемент запрета, управляющий элемент и генератор адресной информации, причем выход аналого-цифрово-. го преобразователя подключен соответст-. венно через элемент запрета ко второму входу сумматора и через блоки апертурного сокращения избыточности по строкам и по столбцам ко входам управляющего элемента и генератора адресной информации, вы ход управ ляющег о элемента соединен со вторым входом элемента запрета, а вцходы генератора адресной информации подключены к синхронизатору и третьему входу сумматора.

485489

Составитель Н Лыс.енко

1екред H.Ханеева Корректор А т ада,сова

Р д ор Т.Фадеева

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24

Заказ 3,03 Изд. р& (gg

Тираж 689 Подписное