Ассоциативное логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 4855Ц (61) Дополнительное к авт. свид-BY (22) Заявлено 18.07. 2(21) 1812861/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.09.75 Бюллетень № 35 (45) Дата опубликования описания27.11.75 (51} М. Кл.

С- llс 15/00

Гасударственный намитет

Совета Министров СССР

t,o делам изоорвтений и открытий (53) УДК 681.327.66 (088. 8)

/ (723 Авторы изобретения

E. П. Балашов и Г. А. Петров (71) Заявитель

Ленинградский ордена Ленина электротехни еский институт им. В. И. Ульянова (Ленина) (54) АССОЦИАТИВНОЕ ЛОГИЧЕСКОЕ ЗАПОМИНАЮШЕЕ

УСТРОЙСТВО

Изобретение относится к запоминающим устройствам (ЗУ)

Известно ассоциативное логическое ЗУ, содержащее числовые линейки, выполненные на магнитных сердечниках, прошитых числовыми шинами записи, считывания и чтения, подключенными к адресным формирователям записи, считывания и индикаторам совпадения соответственно, и разрядными шинами записи, считывания и чтения,под-10 ключенными к разрядным формирователям записи считывания и усилителям чтения соответственно,регистр признака, выходы которого подключены к информационным входам адресных схем И", регистр слова, под- 15 соединенный к регистру маски, выходы которого через разрядные схемы "И" и "ИЛИ" подключены к соответствующим разрядным формирователям записи и считывания, управляющие шины и шины сброса. 20

Эти запоминающие устройства построены на элементах памяти с разветвленным магнитопроводом, производство которых пока недостато но освоено. Кроме того, для хранения одного бита информации при- И меняется по два трансфлюксора и требует ся большое количество оборудования в разрядных цепях.

Цель изобретения — упрощение работы устройства и повышение надежности его работы.

Предлагаемое ЗУ отличается от известного -eM, что оно содержит схемы задержки, дополнительные схемы "И", пары схем

"ИЛИ" и индикаторы регенерации — по количеству числовых линеек, один вход каждой дополнительной схемы "И" подключен к одной из управляющих шин, другой — к выходу соответствующего индикатора регенерации, а выход — к входу схемы задержки и входу одной из пары схем ИЛИ другие входы каждой пары схем "ИЛИ" подсоединены к выходам соответствующих адресных схем "И", а выходы — к входам адресных формирователей записи и считывания, один вход каждого индикатора регенерации подключен к соответствующей числовой шине чтения, а другие — к шине сброса.

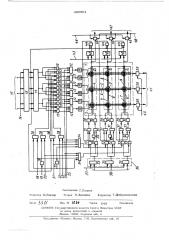

На чертеже изображена функциональная, 1

485501

3 схема предлагаемого ассоциативного логй ческого ЗУ.

Устройство содержит накопитель 1 с числовыми линейками 2 на магнитных сердечниках 3, прошитых разрядными шинами

4 считывания, разрядными шинами 5 записи, разрядными шинами 6 чтения, числовыми шинами 7 записи, числовыми шинами 8 считывания и числовыми шинами 9 чтения, разрядные формирователи 10 записи, разрядные формирователи 11 чтения, разрядные схемы 12 ИЛИ", разрядные схемы «И" 13, регистр 14 маски, регистр

15 слова, шина 16 сброса, входы 17., уп- равляющие шины 18-25, схемы 26 и 27 задержки, схемы 28 "ИЛИ", адресные формирователи 29 записи, адресные формирователи 30 считывания, схемы 31 ИЛИ", схемы 32 задержки, адресные схемы "И"

33, схемы 34 «ИЛИ, триггеры 35 регистра признаков, регистр 36 признаков, шина 37 сброса, входы 38 регистра признаков, усилители 39 чтения, шину 40 стробирования, выходы 41 усилителей чтения, индикаторы 42 регенерации, шину

43 сброса, дополнительные схемы "И«44, индикаторы 45 совпадения, шину 46 odpoca, выходы 47. индикаторов совпадения, шину :48 сброса.

Управляющий вход каждой дополнитель(ной схемы «И" 44 подключен к управляю щей шине 19, информационные входы — к выходу соответствующего индикатора 42 регенерации, а выходы дополнительных,, схем «И«44 — к входу схемы 32 задержки и входу одной иэ пары схем «ИЛИ" 31, другие входы каждой пары схем "ИЛИ 31 подсоединены к выходам соответствующих адресных схем «И«33,, а выходы — к входам адресных формирователей записи

g9 и считывания 30. Информационные входы индикагоров 42 регенерации подсоединены к соответствующим числовым шинам 9 чтения, а управляющие — к шине 43 сброса.

Устройство работает следующим обра, эом. В исходном состоянии в регистре 15 слова хранится входное слово Х {Х, ... К„ у. ,, Хй ), а в каждой числовой линейке 2 накопителя 1 хранится некоторое слово (у,„, g,, g<). Регистр 14 маски находится в состоянии, при котором выделяется -ый разряд входного слова,:а индикаторы 42 регенерации и индикаторы 45 срвпадения — в состоянии «О".

Логические операции, которые могут быть реализованы в предлагаемом ЗУ, выполняются при подаче управляющих сигналов на шину 18 -ь25. l

Операция ассоциативного поиска реали- ( зуется следующим образом.

Реализация операции ассоциативного поиска в данном ЗУ основывается на выполнении операции неравноэначности поразрядно над входным словом и произвольным .маспивом слов, храня щ хся в накопителе., Логическая операция неравноэначности реализуется за два теффта цикла обращения

16 < к ЗУ. В первом такте цикла при подаче управляющего сигнала на шину 22 на выходных числовых шинах 9 чтения формируется сигнал Z (т,,) X ° (, который

15 фиксируется на индикаторах 42 регенерации и индикаторах 45 совпадения, а сердечники 3 числовых линеек 2 переходят в состояния $ ($ ) = g y g . Во втором такте под действием сигйалов с выхода схемы 27 задержки сердечники 3 числовых линеек переходят в состояния g (f,+ .)=х, а на выходной шине 9 чтения наводится сигнал, соответствующий Z {t -7) = „ К„

Таким образом, в одном из двух тактов первого цикла обращения к ЗУ на числовых шинах 9 чтения избранных числовых линеек 2 появляется сигнал, соответствующий выполнению операции сравнения р -го

I разряда входного слова с -ым разрядом каждого из слов, хранящихся в избранных числовых линейках 2, так как

Z-(4 )v Z„(t + )= Х; (; ;У;

Индикаторы 42 регенерации и индикаторы 45 совпадения фиксируют результат сравнения в -ом разряде и в случае несовпадения признаков в данном разряде индикаторы 42 регенерации и индикаторы

45 совпадения соответствующих числовых линеек 2 переключаются в состояние «1«.

Каждый из опрошенных сердечников 3

ro разряда данных числовых линевк 2 принимают состояния, соответствующие результату ; (1,, + 7 ) = Х „

Операция регенерации выполняется так.=1 же в два такта при подаче сигнала на уп- равляющую шину 19 в цикле регенерации.

При этом в первом такте данного цикла при подаче сигнала на управляюшую шину

19 под действием данного сигнала производится опрос вентилей 44, с выходов которых через схемы 3 1 И ЛИ на входы адресных формирователей 29 записи проходят адресные сигналы возбуждения, если индикаторы регенерации 42 находятся в состоянии 1, т. е. в -ом разряде избранных числовых линеек 2 был сформирован сигнал несовпадения Х;) < V X f . Одповременно через управляющую схему 28

4е55О1

1 "ИЛИ" с инверсных выходов регистра 15 ) слова через регистр 14 маски, разрядные схемы И" 13 и схемы 12 "ИЛИ на входы разрядных формирователей 10 записи проходят разрядные сигналы возбуждения

Х = 1. В результате этого в данном такте сердечники 3 опрошенных числовых линеек 2 переходят в состояния (Ф =

y. y Ч а на выходных числовых шинах l

9 чтения наводятся сигналы Е (t Ä= )(.

Е которые подтверждают состояния индикаторов 42 регенерации и индикаторов 45 совпадения.

Во втором такте второго цикла обраще- lб ния через время, определяемое схемой

26 задержки, на его выходе появляется сигнал под действием которого с прямоГо выхода 1, -ro разряда регистра 15 слова, если он находится в состоянии "1 через регистр 14 маски, выделяющий

g -ый разряд, через разрядные схемы

"И" 13 и схемы 12 "ИЛИ" на входы разрядных формирователей 11 считывания проходят сигналы возбуждения Х. = 1. Одновременно с выходов схем 32 задержки через схемы 31 "ИЛИ" возбуждаются адресные формирователи 30 считывания тех числовых линеек 2, индикаторы 42 регезо нерации которых находятся в состояниях "1

Таким образом, во втором цикле обращения — цикле регенерации под действием разрядного и адресных полутоков сердечники 3 t, -го разряда избранных числовых линеек 2 переходит в исходное состояние ; ($ t 7 ) = у, а на числовых шинах 9 чтения наводнтся сигналы Z. (t +

+ L, ) =)(М,, которые подтверждают соФ стояния индикаторов 42 и 45. 40

После выполнения операции сравнения

Р -го разряда входного слова с -ым разрядом каждого из избранных слов индикаторы 42 регенерации при подаче сигнала на управляющую шчну 43 сбрасыва1ат 4б ся в состояние 0", а в индикаторах 45 совпадения зафиксированы результаты сравнения значений g-ых разрядов входного слова и каждого из слов, хранящихся в числовых линейках 2 накопителя 1. 50

Таким же образом реализуется операция сравнения в остальных (— 1) разрядах сравниваемых слов.

После выполнения операции сравнения входного слова с массивом слов, хранимых в накопителе, индикаторы 45 совпадения опрашиваются. При этом на выходах 47 появляются сигналы только с тех индикаторов, котррые остались в исходном состоянии, т. е. код в данной числовой линейке 2 совпал с кодом входного слова.

Предмет изобретения

Ассоциативное логическое запоминаю1

1щее устройство, содержащее числовые линейки, выполненные на магнитных сердечниках, прошитых числовыми шинами записи, считывания и чтения, подключенными к адресным формирователям записи, считывания и индикаторам совпадения соответственно, и разрядными шинами записи, считывания и чтения, подключенными к разрядным формирователям записи, считывания и усилителям чтения соответственно, регистр признака, выходы которого подключены к информационным входам адресных схем "И регистр слова, подсоединенный к регистру маски, выходы которого через разрядные схемы "И" и ИЛИ" подключены к соответствующим разрядным формирователям записи и считывания, управляющие шины и шинысброса,отличающееся тем, что, с целью упрощения устройства и по- вышения надежности его рабрты, оно содержит схемы задержки, дополнительные схемы "И", пары схем "ИЛИ и индикаторы регенерации — по количеству числовых линеек, один вход каждой дополнительной схемы "И" подключен к одной из управляющих шин, другой — к выходу соответствующего индикатора регенерации, а выход— к входу схемы задержки и входу одной из пары схем "ИЛИ", другие входы каждой пары схем ИЛИ" подсоединены к выходам соответствующих адресных схем "И", а выходы — к входам адресных формирователей записи и считывания, один вход каждого индикатора регенерации подключен к соответствующей числовой шине чтения, а другие — к шине сброса.

485501

Составитель Г Па гРов

Редактор Е.Гончар Техред Н.Ханевва Корректор Т.Добровольская

Заказ Я.3 ф Изд. Ха /031 1ираж 648 Подписное

Ц11ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24