Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

ч, QкФФ ффт е ифлиотен

О П И С А Н И Е (ii) 4863I4

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сон)з Советских

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву (22) Заявлено 24,05.73 (21) 1920322/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 30.09.75. Бюллетень № 36 (51) М. Кл. б 06т 5/02

Государственный комитет

Совета евинистров СССР ло делам нзабретений и открытий (53) УДК 681.325.53 (088.8) Дата опубликования описания 05.01.76 (72) Авторы изобретения

А. Ф. Герцовский, С. С. Мухортов и В. А. Орехов (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫИ

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования двоичных чисел в двоично-десятичные.

Известно устройство для преобразования двоичного кода в двоично-десятичный, работающее по принципу сдвига и коррекции и содержащее сдвиговый регистр, разделенный на тетраду. Выходы разрядов каждой тетрады соединены с входами соответствующего блока (деши фратора) коррекции, выходы которого по1дключены к входам соответствующих разрядов той же тетрады. Число блоков коррекции равно, таким образом, числу тетрад в сдвиговом регистре.

Предложенное устройство отличается тем, что выход старшего разряда каждой тетрады сдвигового регистра, кроме первой тетрады, соединен с входом соответствующего элемента

«И» блока коммутации, входы всех тетрад сдвигового регистра, кроме первой и второй тетрад, — с соответствующими управляющими входами устройства.

Это позволяет упростить устройство за счет исключения блоков коррекции для всех тетрад, кроме одной. Исключенное из известного устройства оборудование гораздо сложнее, чем дополнительное оборудование (блок коммутации и источник управляющих сигналов) в предложенном устройстве.

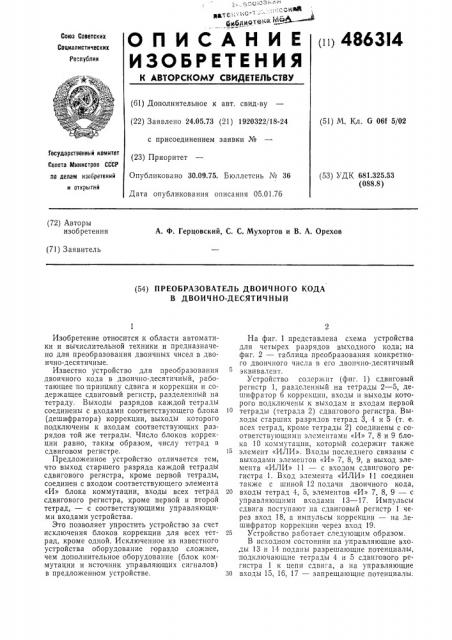

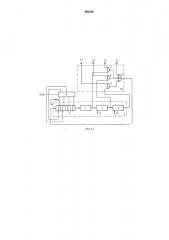

На фиг. 1 представлена схема устройства для четырех разрядов выходного кода; на фиг. 2 — таблица преобразования конкретного двоичного числа в его двоично-десятичный эквивалент.

Устройство содержит (фиг. 1) сдвиговый регистр 1, разделенный на тетрады 2 — 5, дешифратор 6 коррекции, входы и выходы которого подключены к выходам и входам первой тетрады (тетрада 2) сдвигового регистра. Выходы старших разрядов тетрад 3, 4 и 5 (т. е. всех тетрад, кроме тетрады 2) соединены с соответствующими элементами «И» 7, 8 и 9 блока 10 коммутации, который содержит также

)5 элемент «ИЛИ». Входы последнего связаны с выходами элементов «И» 7, 8, 9, а выход элемента «ИЛИ» 11 — с входом сдвигового регистра 1. Вход элемента «ИЛИ» 11 соединен также с шиной 12 подачи двоичного кода, 20 входы тетрад 4, 5, элементов «И» 7, 8, 9 — с управляющими входами 13 — 17. Импульсы сдвига поступают на сдвиговый регистр 1 через вход 18, а импульсы коррекции — на дешифратор коррекции через вход 19.

25 Устройство работает следующим образом.

В исходном состоянии на управляющие входы 13 и 14 поданы разрешающие потенциалы, подключающие тетрады 4 и 5 сдвигового регистра 1 к цепи сдвига, а на управляющие

3() входы 15, 16, 17 — запрещающие потенциалы.

486314

l5

«0 . 5

Входной двоичный код подается, начиная со старшего разряда, по шине 12 через элемент

«ИЛИ» 11 блока коммутации на вход сдвигового регистра 1, сдвигаясь через тетраду 2.

Если число, оказавшееся в тетраде, больше определенного, то это число корректируется.

В данном случае, если число в тетраде 2 больше, чем 4 (т. е. 5, 6, 7, 8 или 9), то к нему прибавляется число 3 в двоичном поле. Прибавление числа 3 (с помощью дешифратора коррекции) может осуществляться как путем сдвига определенных разрядов внутри тетрады 2, так и путем установки разрядов тетрады в определенные состояния.

Пусть, например, преобразуется двоичное число А=0001000111001 (старший разряд записан справа), соответствующее десятичному числу «5000».

Тогда при сдвиге числа А на четвертом такте в тетраде 2 оказьгвается записанным число

1001 (фиг. 2), большее, чем число 4, т. е.

0010 — младший разряд записан слева. В результате дешифратор коррекции переводит тетраду 2 в состояние 0011=7, т. е. прибавляется число 3 к содержимому тетрады (4).

Аналогичным образом осуществляется коррекция содержимого тетрады 2 и в последующих тактов.

Через тринадцать (разрядность числа А) тактов в тетраде 2 записывается младший десятичный разряд искомого выходного числа (в двоично-десятичном коде) . Первый цикл преобразования закончен.

Далее в регистре 1 начинается циркуляция полученного числа А, при этом на управляющий вход 17 подается разрешающий потенциал, число А< сдвигается с выхода тетрады 5 через открытый элемент «И» 9. Сдвиг числа

А< в течение первых четырех тактов осуществляется без коррекции: содержимое тетрады 5 сдвигается в тетраду 2, содержимое тстрады

3 — в тетраду 4 и т, д. (поэтому нумерация тактов на фиг. 2 во втором цикле преооразования начинается с четвертого такта). Ы результате сдвигов и коррекции во втором цикле формируется число А, .полученное в первом цикле искомое значение младшего десятичного разряда оказывается записанным в тетраде 5 (тетрада единиц), после чего на вход 17 подается запрещающий потенциал, а на вход 16 — разрешающий потенциал. 3апрещающий потенциал поступает и на вход 14 тетрады 5, отключая от ее входа цепь подачи импульсов сдвига.

Аналогичным образом происходит преобразование в последующих циклах, причем в течение первых четырех тактов каждого цикла с циркуляцией сдвиг чисел осуществляется без коррекции, а из последующих циклов поочередно исключается по одной тетраде (начиная с тетрады 5) путем запрещения подачи импульсов сдвига, В результате в сдвиговом регистре оказывается записанным двоично-десятичный код исходного числа А, причем старший десятичный разряд — в тетраде 2.

Число циклов преобразования (исключая первый цикл, предварительный) на единицу меньше числа тетрад, а число тактов в каждом цикле (начиная с третьего) на четыре меньше, чем в предыдущем цикле.

Исходное двоичное число может быть записано в регистр и параллельным кодом. В этом случае число циклов преобразования (исключая первый цикл) равно числу тетрад сдвигового регистра.

Управление устройством сводится к регулярному распределению разрешающих и запрещающих сигналов по управляющим вхс дам 13 — 17.

Предмет изобретения

Преобразователь двоичного кода в двоичнодесятичный, содержащий сдвиговый регистр, дешифратор коррекции и блок коммутации, выполненный на элементах «И», выходы которых соединены с входами элемента «ИЛИ», выход последнего соединен с входом сдвигового регистра, вход каждого из элементов

«И» блока коммутации соединен с соответствующим управляющим входом устройства, выходы разрядов первой тетрады сдвигового регистра соединены с входами дешифратора коррекции, выходы которого соединены с входами соответствующих разрядов той же тетрады, отличающийся тем, что, с целью упрощения устройства, выход старшего разряда каждой тетрады сдвигового регистра, кроме первой тетрады, соединен с входом соответствующего элемента «И» блока коммутации, входы всех тетрад сдвигового регистра, кроме первой и второй тетрад, соединены с соответствующими управляющим|и входами устройства.

486314

Исха ньяи д8пичиыи код тысячи

Такт

Еди чщь

Сать и

Десятки

ooo7поа7 !1пп!

П ПО! Опа771ПО

ООО!Ооп!!7О

OOOr OOOr17

ooor ooo«

О7

ОО7

7 îîr

ПП!7

7 007 оо« ! oor

OOr 7

ООО7

1101 о«о

1ОО1

О 7ОО !

0!а

ОПО1 пооо оооо

O0O7OOOr

0007ОПП

000700

О О О!а

9—

1

1171

o«r

r0!

0!О!

0001

000

77 !

2r3Оп о оооо

1ООП !!оо

1!1О

О!а!

1О 7О

0001

7ООО

О!00

1а!о

ООО1 оооо

111 1

o i i 1

7П1 1

ОП!О оопп оооо оооо!

1 оо!и

ПОП! оооо ч

5—

61 000 оооо

oror

0010 оап7

0000 оооо оооо оооо

170о о«о

0011

11--!

2— оооо

1ОО1

1000 оп оооо ! 7OO

О!!О

1ОО1

oroo и!и ооо !

7r О0

010 о оа 70

0700 оооо оооо

7ООО

О1О0

1П10

000 1 оооо пооо оооо

1О1п оооо

Фиг 2

Составитель В. Игнатущенко

Текред М. Семенов Корректор Л. Орлова

Редактор И. Грузова

Типография, пр. Сапунова, 2

Заказ 3208!4 Изд. № 1832 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5