Устройство для выделения переменного приращения

Иллюстрации

Показать всеРеферат

I»I486335

ОПИСАНИЕ

И ЗОБРЕТЕ Н Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свнд-ву ¹ (22) Заявлено 27.04.73 (21) 1913198/18-24 с присоединением заявки № (23) Приоритет—

9IIvoëHêñtâàHo 30.09.75. Бюллетень ¹ 36 (511 .Ч. Кл. 6 061 1 02

Государственный комитет

Совета Министров СССР по делам нзооретений н открытий (53) УДК 68!.34 (088.8) Дата опубликования описания 02.12.76 (72) Автор изобретения

В.М. Тарануха

Таганрогский радиотехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ПЕРЕМЕННОГО

ПРИРАЩЕН ИЯ

Изобретение относится к области вычислительной техники, а именно к цифровым интегрирующим машинам, и может быть использовано в однородных вычислительных средах.

Известны устройства для выделения переменного приращения, состоящее из счетчика, сумматора и регистров. В эти регистры непрерывно перезаписываются накопленные в счетчике числа в прямом (обратном) коде по каждому единичному импульсу приращения.

К концу вычислительного процесса в регистрах записывается сформированный порядок приращения в прямом (обратном) коде.

Подобное выделение переменных приращений в виде порядка старшего разряда приращения с его знаком значительно уменьшает загрузку каналов связи между интеграторами.

Однако сумма выделенных приращений приближается к истинному значению функции к концу вычислительного процесса, если остаток сходится (стремится к нул|о), в то время как на промежуточных этапах вычисления имеет место большая погрешность. Подобное вычисление может привести к появлению погрешности округления, во много раз превышающей истинные значения решения (например, прп решении дифференциальных уравпений).

Цель изобретения — повышение точности вычисления цифровых интеграторов. Для этого в устрой тво введены регистр остатка, блок выделения приращения, блок выделения знакового разряда приращения, блок задержки, IBc схемы выделения порядка приращения, пнверторы, блок запрета знакового разряда, триггер дешифратор. две схемы сборки, блок управления продвижением остатка. Вход и выход регистра остатка подсоединены соответстве н|о к выходу и входу сумматора. Один

10 вход блока выделения приращения подключен к выходу сумматора, один вход блока выделения знакового разряда приращения — к вы ioду блока выделения приращения, а вход блоI<3 задержки — к другому входу блока выделе15 ння знакового разряда приращения. Первые группы входов двух схем выделения порядка приращения соединены с выходом блока задержки, вторые группы входов — с соответствующими выходами первого и второго счет20 чика. Выход одного пз ннверторов подключен к входу первого счетчика, а другого — к группе входоз второго счетчика. Один вход блока запрета знакового разряда подсоединен к входу другого пнвертора, выход — к одному из

25 входов второго счетчика, а другой вход — к выходу третьего инвертора, Один вход триггера соединен с выходом блока выделения знакового разряда, а выходы — с третьими группамп входов схем выделения порядка прираЗ0 щения. Входы первой схемы сборки подключе3

486335

7 — !

0,3 пы к соотве!ствующим выходам схем выделения порядка прира!цеп!и, а выходы — к входам дешпфратора, выходы которого соединены с входами второй схемы сборки. Выходы второй схемы сборки подсоединены к соответствующим разрядам регистра остатка. Выход блока уп1)авлепия продви>кеппем остатка подключен к входу синхронизации регистра остатка, а другие входы блока выделения приращения, триггера, одного из ппверторов, сумматора s! блока продвижения остатка -- к входу устройства. Прп этом приращения, которые меньше кванта (веса младшего разряда подыптегральцой функции) накапливаются в остатке.

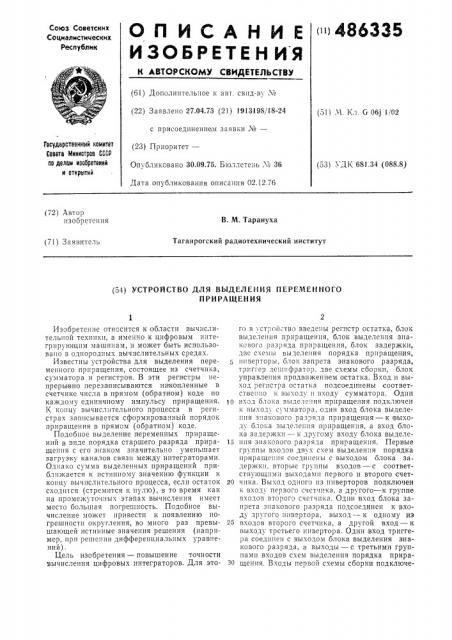

l-la чертеже показана блок-схема устройства, где 1 — 1 !,-! — помер а триггеров регистра остатка приращения; 2 — сумматор, суммирующий остаток предыдущего шага с пеквантовашгь!м приращением; 3 — блок выделения приращения; 4 — блок, управляющий продвижением информации в регистре остатка; 5 — схема сборки; 6 — блок выделения знакового разряда приращения; 7- — триггер, фиксирующий знак приращения; 8 — блок задержки; 9 —; 10 — схема сборки;

11 — схема выделения порядка по,!о>кительного приращения; 12 — схема выделения порядка отрицательного приращения; 13 — пнвертор; 14 — счетчик, формирующий порядок положительного приращения; 15 — ипвертор, 16 — блок запрета прохождения знакового разряда; 17 — счетчик, формирующий порядок отрицателы!ого приращения; 18 — игвертор.

Остаток OS (;+!) имеет переменное количество разрядов и вычисляется по формуле I —

OS(;-:!) =Р-„j (VZ(;,s))-,+OS; !, где (Z(;+!) ), — вычисленное приращепие в дополнительном коде на (;+!)-м шаге интегрирования;

OS; — остаток приращения, вычисленный на !-м шаге иптегрировапи5!;

Р j .. ) z — функция расчленения, выделяющая остаток приращения от — и (мг!адц!!!!! разpsst ) до (! — — 1) р

Минимальный интервал остатка лежит в пределах от — n до — — 1 разряда и хранится в ячейках регистра 1, а максимальньш интервал от — n до (h — 1) разряда и хранится в ячейках регистра 1 — 1 i,-!.

Устройство работает следующим образом.

Перед началом работы регистр остатка переводится из режих!а хранения в режим выдачи информации, путем подачи соответствующих сигналов па вход блока 4, выход которого подключеп к входу синхронизации регистра остатка. Остаток OS; с выхода регистра поступает младшим разрядами в сумматор 2 и суммирустся с приращением (Г7(; i)), 5 !

ЗО

З5

Новый остаток OS (;+!) вводится в освободившиеся к этому времени разряды регистра

1 — 1 (i,-!). В момент выхода из сумматора 2 разряда, представляющего верхпий предел ми. пимальпого остатка, на второй вход блока 3 подается потенциал выделения приращения, который разрешает прохождение сигнала через этот блок. Последу ющие разряды до (h — -1) включительно записываются в регистр остатка и одновременно поступают на входы счетчиков 14, 17 через блок 3 выделения приращепия. В счетчике 14 (формирования IIoрядка поло>кительного приращения) по каждому единичному разряду приращеиия записывается единица во все разряды счетчика, а все последующие нули, включая и знаковый, вычитаются. В счетчике 17 (формирования порядка отрицательного приращения) ка>кды!! нулевой разряд приращения записывает единицы во все разряды счетчика, все последующие единичные разряды вычитаются до зиакового разряда. В момент выхода из сумматора 2 знакового разряда па один из входов блока

6 подается импульс выделения знакового разр5!да, разрец!а5! Те 1! саъ!ыъ! Прохождепие сиг пала в триггер 7. По знаку приращения определяется истинный код порядка приращения.

Наличие блока задержки в схеме позволяет открыть схему 11, когда полностью сформируются коды порядков в счетчиках 14, 17. Если знак приращения положительный, по потенциалам нулевого выхода триггера 7 и импульсом выделения знакового разряда открываетс!! схема 11.

Через открыту!о схему 11 s!a выходные шипы выдается код порядка положительного приращения. Этот же код подается ssa входы дешифратор а 9 и возбуждает определенную шш!у дешифратора, которая устанавливает все триггеры регистра остатка в нуль до (h — 1) разряда включительно, начиная с триггера, в котором хранится единица старшего разряда. В результате, в регистре 1 — 1 (р, !) образуется иовы!! остаток OS (;+!). Если знак приращения отрицательный, то потенциалом с единичного выхода три!гера 7 и импульсом выделения:шакового разряда открывается схема 12. Через открытую схему 12 па выходные шины выдается код порядка отрицательного приращения. Выделепие остатка в этом случае в ре! !!стре 1 — 1 (I ) осуществляется так же, как и при формировании положительIIoI 0 прп ра!цеп!!5!.

Ппедмет изобретения

Устройство для выделения перемеш!ого приращения, содержащее счетчики, сумматор, регистры, отл!! !а(о!цеесл тем, что, с целью повышения точности, в него введены регистр остатка, вход и выход которого подсоединены соответствеппо к выходу и входу сумматора, блок выделения приращения, один вход которого подсоединен к выходу сумматора, блок выделения знакового разряда прираще!!ия, один

48G335

Составитель А. Воронина

Техред Т. Миронова

Редактор И. Грузова

Коррсктор Р. Юсипова

Заказ 2006 Изд Ъ> 1941 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Обл. тип. Костромского уиравлсиия издательств, полиграфии и книжной торговли вход которого подсоединен к выходу блока выделения приращения, блок задержки, вход которого подсоединен к другому входу блока выделения знакового разряда приращения, две схемы выделения порядка приращения, первые группы входов которых подсоединены к выходу блока задержки, вторые группы входов подключены к соответствующим выходам первого и второго счетчика, инверторы, выход одного из них подсоединен к входу первого счетчика, а другого — к группе входов второго счетчика, блок запрета знакового разряда, один вход которого подсоединен к входу другого инвертора, выход — к одному из входов второго счетчика, а другой вход — к выходу третьего инвертора, триггер, один вход которото подсоединен к выходу блока выделения знакового разряда, а выходы — к третьим группам входов схем выделеш|я порядка приращения, дешифратор и две схемы сборки, входы первой из них подсоединены к соответствующим выходам схем выделения порядка приращения, а выходы — к входам дешифратора, выходы которого подключены к входам второй схемы сборки, выходы которой подсоединены к соответствующим разрядам регистра остат«а, блок управления продвижением остатка, выход которого подключен к входу синхронизации регистра остатка, причем другие входы блока выделения приращения, триггера, одного из инверторов, сумматора и блока продвижения остатка подключены к входу устройства.