Постоянное трансформаторное запоминающее устройство

Иллюстрации

Показать всеРеферат

О ИС H E

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пп 486377

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 29.03.73 (21) 1902764/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 30.09.75. Бюллетень № 36

Дата опубликования описания 09.01.76 (51) Ч. Кл. G 11с 17!00

Государственный комитет

Совета Министров СССР ло лелам изобретений н открытий (53) УДК 628 327 6 (088.8) (72) Автор изобретения

В. Д. Горун (71) Заявитель

Научно-исследовательский институт управляющих вычислительных машин (54) ПОСТОЯННОЕ ТРАНСФОРМАТОРНОЕ ЗАПОМИНАЮЩЕЕ

УСТРО Й С1 ВО

Изобретение относится к области вычислительной техники и может использоваться при построении постоянных трансформаторных запоминающих устройств.

Известны постоянные запоминающие устройства, в которых содержатся числовые матрицы с потенциальными и опросными шинами, потенциальные ключи, потенциальные инверторы, каждый из которых через разделительные диоды связан с опросными шинами соответствующей числовой матрицы. Такие устройства обладают недостаточным быстродействием.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в усгройстве выходы потенциальных инверторов связаны через дополнительно введенные резисторы с потенциальными шинами соответствующей числовой матрицы, а одноименные погенциальные шины всех числовых матриц подсоединены через разделительные диоды к соответствующему потенциальному ключу.

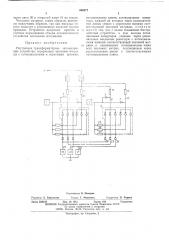

11а чертеже изображена схема предлагаемого устройства.

Устройство содержит потенциальные инверторы 1 и 2, разделительные диоды 3 — 6, опросные шины 7 — 10, числовые матрицы 11 и

12, резисторы 13 — 16, потенциальные ключи

1 7 — 21, потенIIèàëьньк шины 22 — 21, дополнительно введенные резисторы 25 — 27, разделительные диоды 28 — 30.

Устройство работает следующим образом.

В исходном состоянии потенциальные ключи 17 — 21 закрыты, а потенциальные инверторы 1, 2 открыты. 11ри выборке, например, в числовой матрице 12 потенциальный инвертор 2 закрывается, и на его выходе появляегся отрицательный уровень напряжения, запирающий диоды 5 и 6. Этот же уровень через резисторы 25, 26, 27 запирает все диоды в числовой матрице 12. Одновременно или несколько позднее открывается потенциальный ключ, например 21, устанавливающий потенциал, близкий к нулевому, на соответствующей группе потенциальных шин числовой матрицы 12, которая связана с ним через;разделительный диод 30. Диод 30 не препятствует проникновению разрешающего потенциала в числов) ю матрицу 12 от потенциального ключа 21. Вслед за этим потенциальный ключ, например 17, выдает отрицательный опросный импульс, ко" îðûé разветвляется через резисторы 13 и 15. На выходе числовой матрицы 11 он шунтируется через, разделительный диод 3 открытым потенциальным инвертором 1, в то время как развязывающий диод 5 на выходе числовой матрицы 12 заперт, и, следовательно, импульс опроса прохоЗо дит по соответствующей потенциальной шине

486377

Предмет изобретения

Составитель В. Макаров

Техред Т. Миронова Корректор О. Тюрина

Редактор Е. Караулова

Заказ 3239/16 Изд. № 1841 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 через диод ЗО и открытый ключ 21 на землю.

Числовые матрицы, таким образом, включены наилучшим образом, так как импульс опроса подается в защищенные диодами группы проводов. Устройство допускает простое и удобное наращивание объема запоминающего устройства числовыми матрицами.

Постоянное трансформаторное запоминающее устройство, содержащее числовые матрицы с потенциальными и опросными шинами, потенциальные ключи, потенциальные инверторы, каждый из которых через разделительные диоды связан с опросными шинами соответствующей числовой матрицы, отличающ е е с я тем, что, с целью повышения быстродействия устройства, в нем выходы потенциальных инверторов связаны через дополнительно введенные резисторы с потенциальными шинами соответствующей числовой мат10 рицы, а одноименные потенциальные шины всех числовых матриц подсоединены через разделительные диоды к соответствующему потенциальному ключу.