Управляемый арифметический модуль

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслуолик

ОПИСЛНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

11487387 (61) Дополнительное к авт. свид-ву— (22) Заявлено 23.10.73 (21) 1964620/18-24 (51) М. 1с,л, б 06f 7/50 с присоединением заявки—

Государственный комитет

Совета Министров СССР ло делам нзооретеннй и открытий (23) Приоритет—

Опубликовано 05.10.75. Бюллетень ¹ 37

Дата опубликования описания 17.08.7б (50I . 1,K 681.3 5.54 (088.8) (72) Авторы ,изобретения

В. А. Попов, H. В. Кириченко, В. А. Калмыков, И. T. Скибенко и А. В. Сычев (71) Заявитель (54) УП РАВЛЯ ЕМЫ Й АРИФМЕТИЧЕСКИ Й МОДУЛЬ

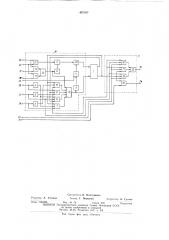

Изобретение относится к области выч:Ic лительной техники и предназначено для ис1пользования в качестве типового элемента при реализации узлов цифровых машин методами интегральной технологии.

Известен управляемый арифметический модуль, содержащий первую логическую схему, выполненную па элементах «И», «ИЛИ» и «НЕ», вторую логическую схему, выполненную на элементах «И» и элементе «ИЛИ», логические и управляющие входы, три-.гер, входы которого соединены с выходами выходных элементов «ИЛИ» первой логической схемы, а единичный выход соединен со Входами первого, второго и третьего элементов

«И» второй логической схемы и входом 7срвого элемента «И» первой логической схемы.

Входы второго элемента «И» первой лоп1ческой схемы соединены с первым управляю щим и,первым логическим входамп модуля.

Входы третьего элемента «И» первой лоп1-Iсcской схемы соединены со вторым упрявля10щих|,и вторым логическим входами модуля.

Третий управляющий зход модуля соедн1гсн со,входом четвертого элемента «И» перзой логической схемы, четвертый — со входом первого элемепта «И» второй логической схемы, выход которого соединен с первым выходом модуля. Третий логический вход модуля соединен со входами первого элемента «НЕ», BåçB0B0 элемента «11» первой логической схс.мы и третьего элемента «11» второй ло;71чсской схемы, четвертый — co входом зто;.0го элемента «И» второй,10".I!÷сской cxc .,1ы.

Выходы второго и третьего элсмечT0tB «И» перBQII;I011гчсс1 Ой cxcмы сОс 7;Iиены со входамп се первого элемента «11,1!1».

Выходы второго,н третьего элсмснтоз «11» зторой логической схемы соединены со Вх0дями ее элемента «11ЛИ», выходы четвертого и пятого элемснтов «II» !ñð1011 логп<1сской схемы сос.7!I!!el!BI со входами сс нсрз0.0 зыходного элемента «11Л11», выходы .1ср- 0Bо, шестого, седы1ого;I зосы1ого элсментоз «11»

1з первой логической cxcxII I сосд:1110:1ы «0 зхадамп ее второго»Ixo7IIO!o элсмс 1тл «11Л11».

Этот модуль реализует 0.107:Iöè! I 101! I lcского сложения и умноже1гия, сдзига 11.1фо,мации влево и BI!ð;IBo, лр:1фметн1сск010 01020 жения и сложс.lllë по модусно дзл, Ip:1смл прямым и обрат;1ым кодом и зыдлчи c0дсржсчмого памяти модуля.

Недо статно 1 BTOI o x!0 >,,1 H 51 B 1 II c- sl 11зб>ь1точное число элементов, связей и зхо lоз модуля, а также организация !!oc,lc IOB11cль:10го переноса прп C.B0>I

Цель изобретения — - упрощение уст;ойства и повышение е-.о быстродействия.

Эта цель достигается тем. что единичный

4873<>7

f CC;Q; V Ct;Q;, П р ед и ет изооретения гср 1 через элементы 5, 11, 0 уста;1азлftз.-.В-,— ся з «0». Одновременно с реализацией функции f на выходе элемента 19 сигнал пере!!оса формируется на выходе 84 модуля при помощи элементов 16, 17, 18 и 23. Таким образом, з мо 1уле реализуется параллельный перенос. что позволяет повысить быстродействие мо<%, i Я.

Для сложения по модулю два на входы 26, 28 подается сигнал а;, на вход 27 — c!ti I!àë а; на вход 82, 33 — константа «0», а на вход

29 — константа «1». При этом на выходе элемента 19 реализуется функция f.которая представляет собой сумму по модулю дза от переменных а; и Q,. При /= 1 триггер устанавливается в ед1шичное состояние, а пр!и f=0 едини<шый сигнал >на выходе элемента 5 через элементы 11, 20 устанавливает триггер в нулевое состояние.

Для приема информации прямым кодом на вход 28,подается сигнал а;, на входы 26, 27, 32 и 83 — константа «0», а на вход 29 — ко11— станта «1».

Переменная а; п!эступает на выход элсмг:1та 19. При а; = 1 триггер 1 устанавливается в единичное состояние, а при а; = О тр: ";ep через элементы 5, 11, 20 — в нулевое.

Лналогично происходит прием информации обратным кодом. При этом на Вход 28 подается сигнал и;, на входы 26, 27, 29 — константа «1», а на входы 82 и 88 — константа «0». ,1ля выдачи содержимого триггера 1 на выход 34,модуля на входы 24, 26, 27 и 28 подается константа «1», а 11а входы 29, 82, и 83— константа «0», При этОм содержимое триггера

1 через элемент «И» 15 поступает на выход 84 модуля. Операция выдачи может быть зыполпена одновременно с любой рассмотренной вышс операцией.

Содержимое триггера может быть стерто раBëè÷íûì .1 способами, в частности при выполнении операции приема прямым кодом при нуле зом сигнале 11а Вхо,е 28.

Упразляемы! : арифметический модуль, содержащий первую логическую схему, Выполненну1о на элементах «И», «ИЛИ», «НЕ», вторую логическую схему. Выполненну1О на элементах «И» и элементе «ИЛИ». логические и управляющие входы, триггер, входы которого соединены с выходами выходных элсменто".

«ИЛИ» .первой логичсско:": с.. смы, а сд>ини<-.ный выход — co входами первого, второго и третьего элемгнтоз «È» зторо1! логичес oй схемы и:входом ",åðâîãî элемента «И» первой логической схемь . входы которого элемента

«И» первой логической схемы соединены с первым управляющим и первым логическим

>;>

СО

65 входами модуля, входы третье,o элемента «И»

-1=рзой логической схемы соединены со вто

pb м упразляющим и вторым логическим Входами модуля, третий управляющий вход соединен с =юдами четвертого элемента «И» первой логической схемы, четвертый управляющ<нй вход модуля соединен со входом перво"o элемента «И» второй ло-,ичсской схемы, выход которого соединен с первым выходом модуля, третий логический вход соединен со входами первого элемента «НЕ», первого эломента «И» первой логической схемы и третьего элемента «И» второй логической схемы, четверть!и логический вход модуля соединен со входом второго элемента «И» второй логической схемы, Bbfxopbi второго и третьего элемснтоз «И» первой логической схемы соедllfleны со Входами ее первого элемента «ИЛИ», выходы второго и третьего элементов «И» второй ло".Il÷ecêoé схемы соединены со входами се элемента «ИЛИ», выходы четвертого и пятого эле, с.t.oB «И» первой логической схемы coe"tIHel ы со входами ее первого выходного эле..:-е11та «ИЛИ», .Выходы первого, шестого, ссдьмого и восьмого элементов «И» первой лог!1:есной схемы соединены со входамп ее второго зыход11ого э.1емента «1IЛИ», о т л ич а ю шийся тем, что. с целью упрощения устройства и позышения его быстродействия, единп шый выход три."гера соед1шен со входом шестого элемента «И» первой логиче" кой схемы. нулевой — co входами седьмого и зосьмо."о элементов «II» первой логической схемы:

B первой логичеокой схеме первый,и второй управляющие Входы модуля соед11нены со входами второго элемента «ИЛИ», выход которого соединен со входом пятого элемента «li»; второй ",ход последнего соединен через второй элемспт «НЕ» с Bbfxoдо ;(первого элемента

«ИЛИ», сосдш1енного также со входом второго выход!юга элемента «ИЛИ», Выход которого;-оеди:e» через третий элемент «НЕ» со вторым входом четвертого элемента «И»; третий логический вход модуля соединен со входом восьмого элемента «И» первой логической схемы !; Входом четвертого элемента «И» зторОй логической схемы. Bbixo.".: которого соедиfIe1 со зхоло>! се элемента «ИЛ1Ь, к зь.xoneó которого подключен второй зыход модуля; выход первого элемента «НЕ» сосдш.ен сп входами шесто-.о и седьмого элементов «I Ь первой лог<ической схемы; четвертый ло-.и-ский ВхО, мод -ля соед:ше:I со BxoxàxiB седьмого элемента «1Ь перзой .-:огической схемы, четвертого B;Iex e!ITB «И» втопой логической схемы и четвер-ого элеме11та «НЕ», выход оторого соединс-t co Bxozaxftt восьмого элемент" «1Ь пепзой логической схемы; пятый у",. ззляю.ций Вход мрдх ля сое.";.111ен со Входом

liIecToI О э !е .> 1! Bxoдом пятого элемента «НЕ», з-.xo-!,.Ioòoðoãо соединен со входом псрзoго элемента «11» первой логической схемы; шестой управляющий вход модуля со динен со входами второго, третьего и четвертого элементов «И» второй логической схемь1.

487387

Составитель В. Игнатущенко

Редактор Д. Утехина Техред Т. Миронова Корректор В. Гутман

Заказ 706!906 Изд. M 79 Тираж 679 Подписное

ЦНИИЛИ Государствеппого комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7Ê,-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Г!атент»