Устройство для синхронизации импульсных последовательностей

Иллюстрации

Показать всеРеферат

0ПИСAНИE 487457

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 02.01.74 (21) 1986636/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 05.10.75. Бюллетень ¹ 37

Дата опубликования описания 24.12.75 (51) М, Кл. Н 03k 5/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.32 (088,8) (72) Авторы изобретения

О. Г. Светников, В. Г. Чибисов и В. М. Гриць (71) Заявитель

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института (54) УСТРОЙСТВО ДЛ СИНХРОНИЗАЦИИ ИМПУЛЪСНЪ|Х

ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к радиотехнике, может быть использовано в устройствах контроля, преобразования, обработки и передачи информации.

Известно устройство для синхронизации импульсных последовательностей, содержащее триггер-датчик опорной частоты, вход которого соединен с шиной опорной частоты, и два каскада синхронизации, каждый из которых содержит схему совпадения, два триггера с раздельными входами, выход первого из которых соединен с одним из входов схемы совпадения, другой вход которой связан с одним выходом триггера-датчика опорной частоты, а выход схемы совпадения соединен с первым входом второго триггера, первый вход первого триггера соединен с шиной импульсной последовательности.

Цель изобретения — повышение чувствительности устройства и ускорение синхронизации.

Для этого каждый каскад синхронизации предлагаемого устройства содержит дополнительную схему совпадения и схему «ИЛИ», первый вход которой соединен с выходом второго триггера, второй вход которого соединен с одноименным входом первого триггера, с выходом дополнительной схемы совпадения, с выходом каскада синхронизации и со вторым входом дополнительной схемы «ИЛИ»; выход этой схемы «ИЛИ» соединен с первым входом дополнительной схемы совпадения, второй вход которой связан с одним из выходов триггера-датчика опорной частоты, а третий ее вход соединен с шиной опорной частоты.

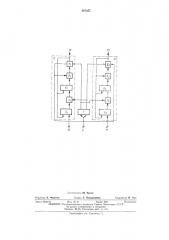

На чертеже приведена блок-схема устройства.

Устройство содержит триггер-датчик опор10 ной частоты 1, вход которого соединен с шиной опорной частоты 2, и каскады синхронизации 3 и 4.

Каждый из каскадов синхронизации содержит соответственно триггеры 5ь 5е, 6ь бе, схе10 мы совпадения 7ь 7., 81, 8е и схемы «ИЛИ»

9ь 9 .

Триггеры 5> и 5е подключены ко входам схем совпадения 7> и 7е соответственно, другие входы которых подключены к выходам

20 триггера-датчика 1. Выходы схем совпадения

7 и 7 соединены с первыми входами триггеров 61 и 6> соответственно. Первые входы триггеров 51 и 5 подключены к шинам 10 и 11 импульсной последовательности соответствен25 но.

Первые входы схем «ИЛИ» 91 и 9е соединены с выходами триггеров 6> и бе соответственно, вторые входы которых соединены с одноименными входами триггеров 51 и 5е соот30 ветственно, с выходами схем совпадения 81

487457

10 и 8 и с выходами 12, !3 каскадов синхронизации 3 и 4.

Выходы схем «ИЛИ» 9>, 9> соединены со входами схем совпадения 81 и 8 . Вторые входы схем совпадения 81 и 8 соединены с выходами триггера-датчика 1, а их третьи входы— с шиной опорной частоты 2.

Работает устройство следующим образом.

Триггер-датчик 1 вырабатывает импульсы, положительные фронты которых отстоят друг от друга на время, равное периоду частоты.

Импульсы частоты с шины 10, поступая на вход триггера 5ь устанавливают его в единичное состояние, при этом с его выхода на вход схемы совпадения 7> поступает разрешающий потенциал. В результате импульсы с единичного выхода триггера-датчика 1 проходят через схему совпадения 71 на вход триггера 61 и устанавливают его в единичное состояние, Разрешающий потенциал с единичного выхода триггера 6i проходит через схему «ИЛИ»

91 и поступает на первый вход схемы совпадения 8ь Следующий импульс опорной частоты перебрасывает триггер-датчик 1 в нулевое состояние, и импульсы с нулевого его выхода поступают на второй вход схемы совпадения

8>. Одновременно импульс опорной частоты поступает на третий ее вход и попадает на выход 12, на второй вход схемы «ИЛИ» 91 и на входы установки в нулевое состояние триггеров 51 и 6ь Последние устанавливаются в нулевое состояние, а схема «ИЛИ» 9i поддерживает на первом входе схемы совпадения 8> разрешающий потенциал на время, равное длительности импульса на выходе 12. В результате на каждый импульс, приходящий на шину 10, устройство вырабатывает на выходе схемы совпадения 8> импульс, длительность которого равна длительности импульса опорной частоты, а передний фронт совпадает с передним фронтом импульса с нулевого выхода триггера-датчика 1.!

Импульсы с шины 11 аналогично синхроннзируются с импульсами с единичного выхода триггера-датчика 1, сдвинутыми относительно импульсов с нулевого его выхода.

В результате на выходах 12 и 13 имеют место две импульсные последовательности, фронты которых синхронизированы импульсами опорных частот и, следовательно, никогда не совпадут во времени.

Предмет изобретения

Устройство для синхронизации импульсных последовательностей, содержащее триггер-датчик опорной частоты, вход которого соединен с шиной опорной частоты, и два каскада синхронизации, кахкдый из которых содержит схему совпадения, два триггера с раздельными входами, выход первого из которых соединен с одним из входов схемы совпадения, другой вход которой связан с одним выходом триггера-датчика опорной частоты, а выход схемы совпадения соединен с первым входом второго триггера, первый вход первого триггера соединен с шиной импульсной последовательности, отличающееся тем, что, с целью повышения чувствительности и ускорения синхронизации, каждый каскад синхронизации содержит дополнительную схему совпадения и схему «ИЛИ», первый вход которой соединен с выходом второго триггера, второй вход которого соединен с одноименным входом первого триггера, с выходом дополнительной схемы совпадения, с выходом каскада синхронизации и со вторым входом дополнительной схемы «ИЛИ», выход которой соединен с первым входом дополнительной схемы совпадения, второй вход которой соединен с одним из выходов триггера-датчика опорной частоты, а третий ее вход соединен с шиной опорной частоты.

487457

Составитель Ю. Еркин корректор Н. Аук

Техред Е. Подурушина

Редактор Б. Федотов

Типография, пр. Сапунова, 2

Заказ 3216/12 Изд. № 31 Тирани 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4 5