Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (!!! 488 255

С;.. Советских

Социалистических

Реса;блин (6!) Дополн!!тельное к авт. свнд-в (22) Заявлено 07.01.74 (21) 1989626/18-2-1 (51) Ч, Кл. G 11с 9, 00

G 06f 13/06 с присоединением заяв !! ¹

Государстееин! !й ка!иитет

Совета Министров СССР ла дела!и изобретений и атхрь!тнй (23) Приоритет

Опубликовано 15.10.75. Бюллетень ¹ 38

Дата опубликования оппсаш!я 29.01.76 53) УД К 681.326. 3 (088.8) (72) Лпторы !!Зобретенпя

П. В. Дербенев, A. A. Виглнн и С Г Иванов (71) Заявитель (54) ЗАПОМИНА1О1ЦЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники.

Известно запоминающее устройство, содержащее накопитель, блоки записи и считывания, регистр и дешифратор. Недостатком известного устройства является низкая информационная емкость, так как большую часть памяти занимает «нулевая» информация.

Цель изобретения — увеличение информационной емкости устройства.

Цель достигается тем, что в устройство введены элементы «И», «ИЛИ», «НЕ», узел сравнения и счетчик, при этом входы устройства подключены ко входам первого элемента

«ИЛИ», выход которого соединен со входом первого элемента «НЕ» и с одним из входов первого элемента «И», выход первого элемента «НЕ» соединен с одним из входов второго элемента «И», другие входы перво;о и второго элементов «И» подключены к шине записи, выходы второго и третьего элементов «И» соединены со входами второго элемента «ИЛИ», выход которого подключен к счетному входу счетчика, выходы счетчика соединены с блоком записи и с одними входами узла сравнения, а другие входы узла сравнения соединены с выходами блока считывания. BI>:êoä узла сравнения соединен с входом второго элемента «НЕ» и с одним из входов четвертого элемента «И», выход второго элемента «НЕ» соединен с одним из входов третьего элемента «И», другие входы третьего и четвертого элементов «И» подключены к шине считывания, выходы первого и четвертого элементов

5 «И» соединены со входами третьего элемента

«ИЛИ», а выход этого элемента соединен с входом регистра и с друптм входом счетчика.

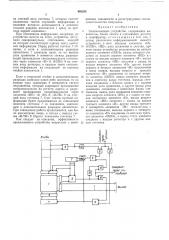

На чертеже приведена функциональная схема предлагаемого устройства, которое содер10 >кит накопитель 1, блок записи 2, блок считывания 3, регистр 4, дешифратор 5, узел сравнения 6, счетчик 7, элементы «И» 8, «ИЛИ»

9, «НЕ» 10.

Устройство работает следующим образом.

15 При записи каждый источник входной информации подключен ко входу ус!!лителя записи отведенного для него разряда накопителя 1. Кроме того, все входные сигналы обьединены на логической схеме «ИЛИ» 9 для

20 управления работой счетчика 7 и регистра 4.

При наличии хотя бы на одном пз входов

«единицы», входная информация и значение счетчика 7 записываются в накопитель 1 и единичный сигнал со схемы «ИЛИ» 9 разре25 шает прохождение сннхроимпульса записи на регистр 4 для перехода в следующем такте к следующей ячейке накопителя 1 и на вход

«сброс» счетчика 7. При отсутствии «единиц» во входной информации схема «НЕ» 10 разре30 шает прохождение синхроимпульсов затзиси

488255

Рхади

Вихор на счетный вход счетчика 7, который считает количество тактов «нулевой» информации и значение которого записывается в дополнительные разряды накопителя 1 сразу по приходе первой «единицы».

При сйисывании информации, например, на устройство "печати из этого устройства поступают синхроимпульсы считывания, каждый из которых соответствует одному такту выходной информации. Перед работой счетчик 7 обнулен, и если в дополнительных разрядах накопителя 1 записаны нули, то на выходе узла сравнения 6 появится сигнал, разрешающий прохождение синхроимпульсов считывания через элементы «И» 8, «ИЛИ» 9 на счетных вход регистра; в каждом такте считывается информация из следующей по порядку ячейки накопителя 1.

Если в очередной ячейке в дополнительных разрядах записано какое-либо значение, то на выходе узла сравнения 6 появляется сигнал несравнения, который запрещает прохождение синхроимпульсов на регистр адреса и разрешает прохождение синхроимпульсов через элементы «НЕ» 10, «И» 8, «ИЛИ» 9 на счетный вход счетчика 7. Счет тактов нулевой информации будет продолжаться до совпадения значения счетчика 7 со значением, записанным в дополнительных разрядах накопителя.

При совпадении работа продолжается, как было рассмотрено выше, и сигнал с выхода схемы «ИЛИ» 9 сбросит показания счетчика 7.

Как следует из описания, эффективность предлагаемого устройства возрастает с повышением скважности в регистрируемых последовательностях импульсов.

Предмет изобретения

5 Запоминающее устройство, содержащее накопитель, блоки записи и считывания, регистр и дешифратор, отличающееся тем, что, с целью увеличения информационной емкости устройства, в него введены элементы «И», 10 «ИЛИ», «НЕ», узел сравнения и счетчик, при этом входы устройства подключены ко входам первого элемента «ИЛИ», выход которого соединен со входом первого элемента «НЕ» и с одним из входов первого элемента «И», выход

15 первого элемента «НЕ» соединен с одним из входов второго элемента «И», другие входы первого и второго элементов «И» подключены к шине записи, выходы второго и третьего элементов «И» соединены со входами второ20 ro элемента «ИЛИ», выход которого подключен к счетному входу счетчика, выходы счетчика соединены с блоком записи и с одними входами узла сравнения, а другие входы узла сравнения соединены с выходами блока счи25 тывания, выход узла сравнения соединен с входом второго элемента «НЕ» и с одним из входов четвертого элемента «И», выход второго элемента «НЕ» соединен с одним из входов третьего элемента «И», другие входы третьего

30 и четвертого элементов «И» подключены к шине считывания, выходы первого и четвертого элементов «И» соединены со входами третьего элемента «ИЛИ», а выход этого элемента соединен с входом регистра и с другим вхо35 дом счетчика,