Устройство для синхронизации импульсов

Иллюстрации

Показать всеРеферат

к

Ч о и и с "х н и е

ИЗОБРЕТЕН ИЯ ") 488320

Союз Советских

Социалистических

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к 381. свпд-и 409353 (5! ) М. Кл. Н 03k 1 16

Н 04! 7т04 (22) Заявлено 02.07.73 (21 ) 1937087 26-9 с прпсоеднпснпсм заявки № (23) Приоритет —Оп бликовано 15.10.75 Бюллетень № 38 осударственный комитет

Совета Министров СССР но делам изооретений и атнрытий (53) УДК 621.374.33 (088.8) Дата опубликования описания 12.05.76 (7?) Автор пзоб)п тс tl tltt

В. П. Ьровикои (7I) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Изобретение относится к импульсной технике. Устройство может использоваться для контроля аппаратуры, для синхронизации цифровых устройств, в которых предъявляются жесткие требования к выработке одиночного выходного импульса независимо от длительности входного.

По основному авт. св. 409353 известно устройство для синхронизации импульсов, содержащее триггер, линию задержки и комбинационную логическую схему в виде последовательно соединенных двухвходовой схемы совпадения и триггера со счетным входом.

Однако это устройство недостаточно надежно в работе.

В целях повышения надежности в работе в предлагаемом устройстве между нулевым выходом и единичным входом триггера включены последовательно соединенные дополнительный триггер и инвертор, а между единичным выходом триггера и входом комбинационной логической схемы включена схема И второй вход которой соединен с входом пнверторя.

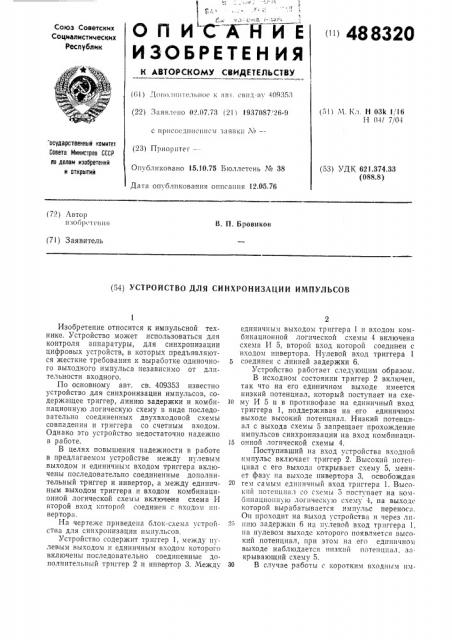

На чертеже приведена блок-схема устройства для синхронизации импульсов, Устройство содержит триггер 1, между нулевым выходом и единичным входом которого включены последовательно соединенные дополнительный триггер 2 и инвертор 3. Между

2 единичным выходом триггера 1 и входом комбинационной логической схемы 4 включена схема И 5, второй вход которой соединен с входом пнвертора. Нулевой вход триггера 1

5 соединен с линией задержки 6.

Устройство работает следующим образом.

В исходном состоянии триггер 2 включен, так что на его единичном выходе имеется низкий потенциал, который поступает на схе10 му И 5 и в противофазе на единичный вход триггера 1, поддерживая на его единичном выходе высокий потенциал. Низкий потенциал с выхода схемы 5 запрещает прохождение импульсов синхронизации на вход комбпнаци15 онной логической схемы 4.

Поступивший на вход устройства входной импульс включает триггер 2. Высокий потенциал с его выходя открывает схему 5, меняет фазу на выходе ннвертора 3, освобождая

20 reit самым еднпичпьш вход триггера 1. Высокий потенциал со схемы 5 поступает на комбинационную логическую схему 4, на выходе которой вырабатывается импульс перенося.

On проходит на выход устройства и через ли2 нпю задержки 6 ня нулевой вход триггера 1, па нулевом выходе которого появляется высокий потенциал, при этом на его едшгичном выходе наблюдается низкий потенциал, зя. крывающий схему 5.

30 В случае работы с коротким входным нм488320

Составитель E. Погиблов

Т<«род E. Подурушина

Корректор Л. Котова

Р дактср "f. Юриикова

Изд. М 1906 Тираж 902

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7Ê-35, Раушская наб., д. 4/5

Заказ 542

Подписное

МОТ, Загорский филиал пульсом высокий потенциал с нулевого выхода триггера 1 выключает триггер 2, возвращая его в исходное состояние, и включает триггер 1. На схеме 5 высокий потенциал при переключении триггера 1 не появляется, так как прежде на втором входе схемы 5 появляется «0» с три1тера 2.

При работе с протяженным входным импульсом после того, как на нулевом выходе триггера 1 появляется высокий потенциал, пи обоих входах триггера 2 поддерживается «1».

Гхема 5 закрывается низким потенциалом единичного выхода триггера 1. По окончании входного импульса выключается триггер 2, поддерживая схему 5 в закрытом состоянии.

На выходе инвертора 3 появляется «1», включающая триггер 1.

При поступлении следующего входного импульса цикл повторяется.

Предмет изобретения

Устройство для синхронизации импульсов по авт, св. 409353, отличающееся тем, что, 10 с целью повышения его надежности в работе, между нулевым выходом и единичным входом триггера включены последовательно соединенные дополнительный триггер и инвертор, а между единичным выходом триггера и входом

1," комбинационной .тогической схемы включена схема И, второй вход которой соединен с входом инвертора.