Устройство отладки программ для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (><)409107

ИЗОБРЕТЕН Ия

Союз Советских

Социалистических е еслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено24 11.72 (21) 1849888/18-24 (51) M. Кл. С. 06 ) 11/00 с присоединением заявки №вЂ” (23) Приоритет(43) Опубликовано 25 10 75,Бюллетень № 39 (53) УДК 628.327.66(088.м.) (45) Дата опубликования описания07.01. 76

Государственный квинтет

Сеавта Министров СССР не делам изобретений н открытий (72) Авторы изобретения

Т. Ф. Аверьянова и А. Ф. Соколенко (71) Заявитель (54) УСТРОЙСТВО ОТЛАДКИ ПРОГРАММ ДЛЯ

ПОСТОЯННОГО ЗАПОМИНАЮШЕГО УСТРОЙСТВА

Изобретение относится к вычислительной технике.

Известны устройства отладки программ для постоянного запоминающего устройства, содержащие блок приема и вывода команд, первые входы которого соединены с выходами блока подключения постоян ного запоминающего устройства (ПЗУ), вторые входы — с выходами и входами запоминающего устройства без разрушения информации (ЗУБРИ), а выходы — с числовыми шинами, блок управления, входы которого соединены с адресными шинами и командной шиной обращения, а первые выходы — с первыми входами блока формирования адреса, вторые входы которого связаны с адресными шинами, а выходы

;блоком подключения постоянного запоминающего устройства..

Бель изобретения — повышение точ. ности работы устройства. Достигается это тем, что устройство содержит распре. делитель, блок формирования адреса участка и блок регистров установки, причем первые выходы распределителя соединены с соответствующими входами ЗУБРИ, вто рые выходы и третьи входы с входами блока подключения ПЗУ, первые входыс блоком управления, вторые - регистром установки, третьи — с блоком формиро1

; вания адреса участка, входы которого . соединены с выходом блока управления и адресными шинами.

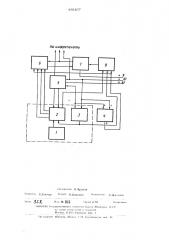

10 На чертеже. приведена схема устройства.

Предлагаемое устройство содержит блок 1 регистров установки; распределитель 2, блок 3 формирования адреса участка, блок 4 ф .рмирования адреса, блок 5 управления, запоминающее устройство 6 без )разрушения. информации, блок 7 приема и вывода команд, блок 8 подключения

Т 4, и постоянного запоминающего устройства (ПЗУ), числовые шины 9, адресные шины

1 0 и командную шину 1 1 обращения.

Устройство работает в режимах р аб оты с электронной вычислительной машиной (ЭВМ), автоматической перезаписи

g5 участка, однократной записи по адресу, 489107 однократного считывания по адресу и вы-1 дачи информации на печать.

Включение того или иного режима осуществляется с помощью блока управления 5, органы управления которого выведены на переднюю панель устройства, Для обеспечения перебора адресов в режимах автоматической перезаписи или выдачи информации на печать блока 3 и

4 содержат счетчики адреса из блока 4 в счетчик блока 3, Импульсы счета поступают на первые входы блоков 3 и 4 с первого выхода блока управления 5 в режимах автоматической перезаписи или режима выдачи информации на печать. При этом, в блоке 3 формирования адреса участка и в блоке 4 формирования адреса запрещается прием кодов адреса, поступающих из ЭВМ, а в распределителе 2 при совпадении кодов разрядов адреса ПЗУ; поступающих из бло- ков формирования адреса участка 3 и с регистров установки 1, происходит выдача на первые выходы. кода адреса ЗУБРИ, а по второму выходу — признака считывания из из ПЗУ, и происходит перезапись чисел, 25 считываемых из ПЗУ и поступающих через блок 7 приема и вывода. команд на числовые входы ЗУБРИ 6. по всем адресам, старшие разряды которых совпадают с кодами, выбранными на регистрах 1 (младшие разряды поступают на первые адресные входы блоков подключения ПЗУ и ЗУБРИ со схемы 4 приема и формирования адреса). Блок

7 приема и вывода по сигналам из блока управления 5 осуществляет, кроме комму- З5 тации считанной информации из блока подключения ПЗУ 8 в блок ЗУБРИ 6 в режиме автоматической перезаписи участков, коммутацию считанной информации из блока 6 или из блока 7 на числовые шины 9 под- 4О ключения ЭВМ (в режиме работы с ЭВМ) или на шины подключения печати (в режиме выдачи информации на печать.).

0ля обеспечения выбора адреса в однократных режимах блоки формирования 3 45 и 4 содержат тумблерные регистры установки адреса. При однократной записи по адресу, выбираемому на регистрах установки адреса блоков 3 и 4, код числа набирается на тумблерном регистре, входящем 50 в состав блока 7 приема и вывода команд. При поступлении на ЭВМ кода адреса ПЗУ часть разрядов поступает через блок формировании адреса на адресные вхо ды блока подключения ПЗУ и ЗУБРИ, Ос- 65 тальные разряды адреса через блок 3 формирования адреса участка поступают на входы блока ПЗУ и на;входы распределителя 2, где сравниваются с разрядами регистров установки 1. При сравнении на распределителе 2 разрядов адреса с состоянием одного из регистров установки 1, с первых выходов распределителя 2 поступает на ЗУБРИ 6, код адреса учас гка, соответствующий порядковому номеру этого регистра, При этом из распределителя 2 на на вход ЗУБРИ 6 поступает признак считывания, если блок управления 5 по первому выходу выдает разрешение считыва ния (в режиме работы устройства с ЭВМ, в режиме однократного считывания по адресу или в режиме выдачи информации на печать), или разрешение записи. При сравнении в распределителе 2 кода адреса с состоянием одного из регистров 1 импульс, обращения к ПЗУ на втором выходе распределителя 2 не вырабатывается и вход блока подключения ПЗУ запрещается. Про.хождение. этого сщ нала разрешается при несовпадении кода адреса участка из бло ка,3 с состоянием ниодного из регистров

1 установки. При этом запрещается прохождение признаков записи. или считывания на первые выходы распределителя 2 и далее на входы ЗУБРИ 6, Предмет изобретения

Устройство отладки программ для постоянного запоминающего устройства, содержащее блок приема и вывода команд, первые входы которого соединены с выходами блока подключения постоянного за поминаюшего устройства, вторые входы с выходами и входами запоминающего устройства без разрушения информации, а выходы — с числовыми шинами, блок управления, входы которого соединены с адресными шинами и командной шиной обращения, а первые выходы — с первыми входами блока формирования адреса, вторые входы которого связаны с адресными шинами, а выходы с блоком подключения постоянного запоминающего устройства, о тл и ч а ю ш е е с я тем, что, с целью повышения точности работы устройства, оно содержит распределитель, блок формирования адреса участка и блок регистров установки, причем выходы распределителя соединены с соответствующими входами запоминающего устройства без разрушения информации, вторые выходы и третьи входы — со входами блока подключения постоянного запоминающего устройства, первые входы — с блоком управления, вторые - с регистром установки, третьи — с блоком формирования адреса участка, входы которого соединены с выходом блока управления и адресными шинами.

489107

Ип u@ponevomb (;Оста ни1()4ь 13.ej>poJtoB (Iс)г(чд11 1ех1>е (11.)(г)неевя 11О1»(- > г ll) д 11„)((>г)(1

1)ела кт()1) 11олн) спое

Зака)) 3gg И;>л. pa ///$ 1 5(1>а)к 1)79

l ll l11llI 111 I oñóËàI>ñòâåíHoão t;(>it)i tet Со>5() а Mt(t(tt(t I>()«(.;(. 1:1 но лс>5((м it)()(>11 ll litt)i н (>il)I)llr

Мискна, 11;I(I3;>, 1 ay>it(:t (»t н))с)., 4

I II> .et )1>tt » Гнс 411а ri .it r, МО(к>)5), I >15, 1>(1)(н(к(>()с) tl 5(tt (It>, - о4