Устройство для изменения масштабов в аналоговых вычислительных машинах

Иллюстрации

Показать всеРеферат

Щф т . 1, био 77: : —::-ОП и й

Сс 703 Советских

Социалистических

Республик

КЗОБРЕ-:ЕК ". -,: ! g А87QP<@GМУ СВЫДЕТБЛЬС - =Y с

1, 5j) Дополнительное к ав=. сзнд-ву

1 (22) Заявлено 24.08.74(Е) 2С36597/:-8-24 с прксоедттиениетк аа.":вкя га

) (23) НРаОР1ТеТ

1 (4З) Оп,„блнковано 2 -, д —, -ю77„е е-,ь т g

) (Я) Д ата опуоднкованяя опнсанття Я

ГНаударатвнннь7Й нммнтет

6088ТВ Мнннл 7аа Щ1 по делам нзабретнннй н ютнрытнй (72) ABTOPb изобретения

МЧВНОВ М В Г (gg) У т рщс-,где r7är. Ир 7=Н=-;-Ис(р;„ . 777 д,-д8

Ä77 аД ) . 7-7P .. 71 Ц Д Я +1+7» „. ) » P„77Ò71 7 Л Ъ;

: —,оров вычттслительного блока., меняюшнхся ат задачи к задаче и От варианта к варио акту при и Оведентцт на аналоговой 7 ташкее исследованттй, ."7.0о..:e того.;количество:т-х

Определяется чттc:.!á:"ë псдцнапазонов, Ба кс

aopLIG Вазбивается мвсштабкру емая переменная. Бходнь1е p 3HTo üi касто.: ".ваюTся на спецкальнь7х !:Тьтах, 7 поэте.".;у тОч ность их настройки зависит От Опыта оператора к качества настроечной аппаратуры. При этом П77оцесс настройки требует определенного времени, что увеличивает обшее время подготовки задачи к решению.

С целью повышения точности к быстроi5 действия в устройство дополнительно введены дифференцируюшие блоки, элемент задержки, элементы И 7; ИЛИ, запоминвюшие регистры, регистр цкфро управляемых сопротивлений, кл7очевые элементы, прк.-:ем вторяк группа выходов реверсивнсго счетчика импульсов сс динена через блокидифференцированкя и элемент задержкисовторымн входами элементов И, первые входы которых подсоедкнечы K выходам соответств чошкх разрядсв запомкнаюшего регкстУстройство для изменении масштабов в аналоговых вычислительных MGJiHHpx GTНОСИТСЯ К .ВЫЧИСЛИТЕЛЬНой ТЕХНККЕ К, В «ВСТ ности, к аналоговым вычислительным машинам.

Известно устройство для изменения масштабов в аналоговых вычислительньт» машинах, содержашее интегратор, вь-ход которого через бло., фиксации границ диапазона и блок блокировки ложного импульса подсоединен ко входу реверсивногосчетчика импульсов, первая группа выходовкоторого подсоединенв к индикатору; вход инте;-ратора подсоединен к коммутирующей части блока сброса и задания начальных условий, выход которого подсоединен к блоку фиксации знака машинной перемечной, выход блока фиксации знака машинной переменной подсоединен к управляюшей части блока сброса и задания начальных условий, выход которогс подсоединен к коммутируюшей части блока сбросе и задания начальных условий.

Недостатком известного устройства является наличие различных входных резкс((. -) 4Э93. х 8 (1

1

7

7 (5!l М. ХЛ.606(7".iОС

7

7

7

1 (кч 7 Д т 88 7 ЯЯ "7, (088.8 j

489118 ра, выходы элементов И подсоединены к первым входам соответствующих разрядов регистра цифро-управляемых сопротивлений, а выход каждого разряда регистра цифро-управляемых сопротивлений подсоединены к управляющим входам соответствующим ключевых элементов, выходы которых подсоединены ко входу интегратора, вторые входы соответствующих разрядов цифро-управляемых сопротивлений через элемент

ИЛИ соединены с выходами блока дифференцирования.

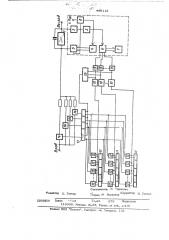

На чертеже приведена блок-схема устройства для изменения масштабов в аналоговых вычислительных машинах, Устройство содержит интегратор 1, блок

2 фиксации границ поддиапазона, блок 3 блокировки ложного импульса, 1лок 4 сброса и задания начальных условий (управляющая часть, блок 5 сброса и задания начальных условий (коммутчруюшая часть), реверсивный счетчик импульсов 6, индикатор поддиапазонов 7, блок 8 фиксации зна» ка машинной переменной, дифференцирующие блоки 9, элементы задержки 10, запоминающие регистры 11 ° элементы И 12, регистр цифро-управляемых сопротивлений 1 3, ключевые элементы 14, элемент ИЛИ 15.

Устройство для изменения масштабов в аналоговых вычислительных машинах работает следующим обр."эом.

При пересечении машинной переменной границ поддиапазона срабатывает блок 2 фиксации границ поддиапазона, выдающий импульс напряжений для запуска управляющей части 4 блока сброса и выставки начальных условий, который с помошьюсвоей коммутирующей части 5 разряжает емкость интегратора 1 и заряжает ее напряжением нового начального условия для следующего поддиапазона.

Для ликвидации срабатывания остальных блоков устройства от ложного импульса, образующегося во время операции смены масштаба, идущего от блока 2 фиксации границ поддиапазона (в зависимости отхарактеров изменения выходного напряжения интегратора 1 Р, предусмотрен блок 3 блокировки ложного импульса. Одновременно с запуском блока сброса и выставки начального условия 4 импульс напряжения отблока фиксации границ поддиапазона поступа- . ет на реверсивный счетчик импульсов 6, что приводит к срабатыванию индикатора поддиапазонов 7. При отрицательном знаке масштабируемой переменной срабатывает блок фиксации знака машинной переменной

8, воздействующей на блок 2 фиксацииграниц поддиапазона для работы с отрицательным знаком машинной переменной, а также подключающий отр ательное опорное напряжение, используемое для формирования напряжения начального усло вня. С рабат ывание реверсивного счетчика импульсэв 6 приводит к выдаче с его вторых выходов импульса на соответствующий дифференцируюший блок S, который преобразуется им в запускающий импульс. Этот импульс проходи; на.соответс вующий элемент задержки 10 и на элемент ИЛИ 15, Элементзадержки служит для разделения во времени импульсов, поступающих на управлениезапоминаюшими регистра.. и 11 и на выполнение операции сброса регистра цифре-управляемых сопротивлений 13, что осуще< увляется с подачей импульса с выхода элемента ИЛИ 15 на входы установки нуля разрядов этого регистра. С выходаэлемента задержки 10 запускающий импульс проходит на вторые входы элементов И 12 запоминающего регистра ll соответст уюшего поддиапазона, в который переходит машинная переменная. Так как первыевходы элементов И 12 подсоединены к выхо-„дам соответствующих разрядов запоминающего регистра 11, то по приходе запускающего импульса информация, заложенная а нем (значение передаточного коэффициента интегратора 1 по масштабируемой машиной переменной соответству ющего поддиапазона), устанавливается н регистре цифро-управляемых- сопротивлений 13. С

35 . этого регистра сигнал управления поступает на соответствующие ключевые элементы 14, подключающие входные резисторы интегратора и дающие в сумме пе-редаточный коэффициент по машинной переменной, соответствующе поддиапазону, в который она переходит и значение которого было заложено в оответствующем запоминающем регистре 11, Значение входных резисторов подбираются так, чтобы B сумме обеспечивался любой передаточный коэффициент интегратора l. При переходе машинной переменной в другие поддиапазоны процесс выставки передаточных коэффициентов проходит аналогично.

Формула изобретения

Устройство для и=менения масштабов

B аналоговых вычислительных машинах, содержащее интегратор, выход которого через блок фиксации границ диапазона иблок блокировки ложного импульса подсоединен ко входу реверсивного счетчика импульсов, первая группа выходов которого подсоеди489118 нека к индикатору вход интегратора подсоединен к ком.:у-гируюшей часги блока сброса и задания начальных условий, выход которого подсоединен к блоку фиксациизна ка машинной переменной, выход блокафиксг. ии знака машинно) переменной подсоединен к управляюшей части блока сброса и задания начальных условий, выход которого подсоединен к коммутируюшей частиблока сброса и задания начальных условий,о тл и ч а ю ш е е . я тем, что, с целью повышения точности и быстродействия, в устройство до| олннтельно введены дифференцируюшие блоки, элемент задержки, элементы И и

ИЛИ, заломинаюшие регистры, регистрцифро-у равляомых сопротивлений, ключевые элементы, причем вторая группа выходов реверсивного счетчика импульсов соединена через блохи дифференцирования и элемент задержки со вторыми входами элемента К, первые входы которого подсоединены к выходам соответствуюших раэ">ядов запоминаюшего регистра, выходы элементов К

:подсоединены к первым входам соответст-. вуюших разрядов регистра цифро-управляемых сопротивлений, а выход каждо о разо ряда регистра цифра-управляемых сопротив-. лений подсоединен к управляюшим входам соответствуюших. ключевых элементов, выходы которых подсоединены ко входу интегратора, вторите входы соответствуюших разрядов цифро-управляемых сопротивлений через элемент ИЛИ соелинены с выходами блока дифференцирования.

Редактор Е. Гончар

С .оставитель Н ТаРасова

КоРРектоР К. Гоксич

Техред М ЛевиикаЯ щц.ущИ 3аказ 1 g Тираж 679 Подиисное

113035, Москва, Ж-35, Раушс ая наб., д.4/5 филиал ППП Патент», Ужгорсд, v агарина, 101