Адаптивная вычислительная система обучения

Иллюстрации

Показать всеРеферат

1

ОП И-Ю-АНИЕ

ИЗОБРЕТЕНИЯ

,. с к> > с, > >> а >.-;, > н (11} 4Я9139 оццb > и> и>>>сс> >> т еспубпик

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б>1} Дополнительное к авт. свид-ву (22) >зявлено28.05.74 (21) 2029054/18-24 (51) М. Кл.G 0; Ь,/00 с присоединением заявки ¹

Гос)>даротвеиив>й номитет

Соввтв Министров СССР по делам изооретений и открытий (2.>) (1pHOpl!TPT )публиковано25 10 75,Бюллетень № 8с> (53) УД К 6 81.3.07 6 (088.8) Дата опубликования описания 25.10.75> (72) .Автот изобретения

М, И. Соболевский (73) заявитель

ЛДЛПтИВНДЯ БЫЧИСЛИтБЛЬНЛЯ CHCTEMA

ОБУЧЕПИЯ (54 ) Изобретение зги> с.игсл к автоматике и вычислительной технике, в частности к адаптивнь>м вычиспигельным системам BC обучения.

Известная адаптивнал вычислительная система обученил сс>держит блок оценки степени адаптаций, п»дключенный к блоку связи и к блоку управления адаптацией, последовательно соединенных между собой.

Однако известное устр >йство не о>>еспечивает адаптацию по то чс>сти (разрядности) представпенпя входной информации, используемой при ре.пении задач обучения.

Кроме того, не обеспечичается в прототипе адаптация и по таким параметрам как набор операций по решению задач, состояние объекта (обучаемого ) по времени.

Кроме того, эффективность испопьзова- ) ния составных частей прототипа при решении малых задач лвпяетсл низксй. 20

Пель изобретенил — пс>вьш>ение эффективI ности процесса обучения.

Дс>-тигаетсл э > те..ь !т> система со>--.>>mHT б > к а:>аптаппи по разряд— ности ввоаи">ой »нфс>р>>аппп, блок адаптации по набору операций, последоватепьно соединенные между собой, блок адаптации по состоянию обучаемого и блок временной адаптации, входы которых подключены к блоку управления адаптацией, а выходы — к блоку оценки степени адаптации. Блок адаптации по разрядности вводимой информации содержит узел анализа длины входных фраз, узел определения признака исходных данных, узепвыбооа способа адаптации, выходы которого соединены с узлами анализа длины входных фраз и определения признака исходных данных, узды настройки устройства памяти и вычислителей по:разрядности, входы которых соединены с узлами анализа длины входных фраз и определения признака исходных данных. Блок адаптации по набору операций содержит последовательно между собой узлы выбора способа адаптации по набору микрокоманд, анализа кодов операций и настройки устройства микрокоманд управляющего процессора.

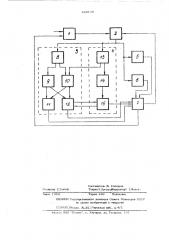

На чертеже приведена структурнаясхема адаптивной вычислительной системы.

Она содержит блок 1 связи вычислительной системы с конечными устройствами, блок 2 управления адаптацией, блок 3 адаптации вычислительной системы по разрядности вводимой информации, блок 4 адаптации по набору операций, обеспечивающих решение задачи, блок 5 адаптации по состоянию объекта (обучаемого)„ блок 6 временной адаптации, блок 7 оценки степени адаптации, Блок 3 содержит узел 8 и выбора способа адаптации по разрядности информации, узел 9 аналгза-,входных Фраз1 по их длине, узел 10 определения признака исходных данных по разрядности вход-, ной информации „зел 11 настройки устройства памяти вычислительной системы разрядности, узел 12 настрсйки вычислителей по разрядности.

Блок 4 включает узел 13 выбора спо- ж саба адаптации по набору микрокоманд, обеспечивающих решение задачи, узел 14 анализа кодов операций, которые необходимо выполнить для решения задачи. и узел 15 настройки устройства микрокоманд- рк управляющего процессора вычислительной системы, В статике элементы адаптивной вычислительной системы обучения взаимосвяза- . Э) ны следующим образом, Вход блока 1 свя-, зан адаптивной вычислительной системы соединен с конечными устройствами (пультами обучаемых), а выход — с блоком 2 управления адаптацией. Выход блока 2 управ= @ ления адаптацией соединен с входами блоков 3 - 6, обеспечивающих адаптацию вычислительной системы обучения по различным параметрам, Выходы блоков 3 - 6 соединены с входом блока 7 оценки степени адаптации вычислительной системы обучения по одному или нескольким параметрам.

Один выход блока 7 соединен с блоком 1, а второй — с блоком 2. !

В блоке 3 узел 8 соединен с узлами

9 и 10. Блоки 3 и 4 связаны также между собой через узлы 10, 13 и 12, 15, Узлы 9 и 1 0 соединены с узлами 1 1 и

12. Выходы последних.являются, выходом блока 3 и соединены с блоком 7.

В блоке 4 вход узла 13 являетсявходом блока 4, Один из выходов узла 15 соединен с блоком 7. 55

Система работает следующим образом.

Объект (обучаемый) с конечного устройства обращается к вычислительной системе через блок 1. Блок 2 анализируетдан- 66 ные о задаче, историю решения за-ачданного класса, состояние (настройку) блоков

3 - 6 и другие данные, необходимые для принятия решения об адаптации системы по одному, нескольким яли всем параметрам, а именно по разрядности (например, по точносги решения задач пля длине при= нимаемых и обрабатываемых „раз обучения); по выбору операций, которые необходимо выполнить, чтобы решить ъадачу (например, только логические, или только арифметические, или -,е и другие, но в различных соотношениях) ", по состоянию объекта (на ример, техническое состояние конечного устройства или биологическое психическое, интеллектуальное, физическое состояние Обучаемого); rc времени (например, по быстродействию решения задач, по длине отрезков временимежду выдачей кадрод информации обучаемому).

Блок 2 вырабатывает управляющиесигналы на блоки 3-6, которые настра,— вают память, вычислители и управляющий процессор на необходимые параметры. Результаты B&cTpoAKH анализируются оло » ком 7 и в случае удовлетворительнойнастройки (степень адаптации удовлетворяет заданным критериям), выдает сигнал на блок 1, в результате происходит решение задачи использованием только такого кс личества оборудования вь|числительной си= стемы, которое необходимо для решения данной задачи, Если степень адаптация неудовлетворительна, то блок 7 передает управление на блок 2 и процесс перестройки устройств продолжается. При этом используется информация из истории настройки ВС и решения задач, подобных данной, Особенность работы блока 3 в процессе адаптации заключается в том, что узел 8, пользуясь информацией о задаче от блока

2, определяет присутствие признака разряд- ности исходных даниых. Так, для многих задач заранее известно с какой точностью их необходимо решать, т.е. известно какую разрядность должны иметь вычислитель и память вычислительной системы. Если признака нет, то управление от узла 8 передается к узлу 9, который анализируетвходные данные и другие признаки и определяет необходимую разрядность (точность) решения задачи. Если признак есть, тс от узла 8 управление передается к узлу 1 О, который определяет конкретное значение признака и по нему необходи.иую разрядность (точность ) решения задачи „После определения необходимой "гочности решения зада4891 39 чи„узлы 11 и 12 настраивают память и вычислители на необходимую разрядность.

Блок 4, получив команду на настройку вычислительной системы по набору операций, выбирает способ адаптации, Если заявка на решение задачи имеет признак набора операций (например, заранее извесь но, что для решения данной задачи необходимы только логические операции), то управление с узла 13 передается на узел -O, К

B далее BpGBcxogRT настройка,вычислите лей и памяти как описано, Если признака нет, то управление передается на узел 14, который анализирует операции, несбходимые для решения задачи, и передает управление Ы узлу 15. Последний организует настройку устройства микрокоманд управляюшего проц ССОра т&К, Что для рЕШЕНИя д&ННсй Задачи набирается совокупность микроком&нд, обеспечиваюших решение задг-чи. Кроме Ж

I того, узлы 12 и 15 обмениваются информацией при настройке с целью взаимной коррекции пар&метр в.

Таким образом совместная работа всех блоков и узлов вычислительной системы увеличивает ее адаптивные возможности повышает эффективность использования (степени загрузки) элементов системы.

\ 30

Предмет изобретения

1. Адаптивная вычислительная система обучения, содержашая блок оценки степени адаптации, подключенный к блоку связи и

И к блоку управления адаптацией, последовательно соединенных между собой, о т л ич а ю ш а я с я тем, что с целью повышения эффективностн процесса обучения, система содержит блок адаптации ло разрядности вводимой информации и блок адаптации по набору операций, последовательно соединенные между собой, блок адаптации по состоянию обучаемого и блок временной адаптации, входы которых подключены к блоку управления адаптацией, а выходы — к блоку оценки степени адаптации.

2, Система обучения по и. 1 о т л ич а ю ш а я с я тем, что блок адаптации по разрядности вводимой информации содержит узел анализа длины входных фраз, узел определения признака исходных данных, узел выбора способа адаптации, выходы которого соединены с узлами анализа длины входных фраз и определения признака RcxoQHblR данных, узлы настройки устройства памяти и вычислителей по разрядности, входы которых соединены с узлами анализа длины входных фраз и определения признака исходных данных.

3, Система обучения по и. 1 о т л ич а ю ш а я с я тем, что блок адаптации по набору операций содержит последовательно соединенные между собой узлы выбора способа адаптации по набору микрокоманд, анализа кодов операций и настройки устройства мнкрокоманд управляюшего прон,ес.сор а .

Редактор Г.Гончар

Заказ 1 084

Составитель В. Гончаров

ТехредО. ЛуговаЖорректор 3. Фэнта

Тираж 496 " Подписное

ИН1П1ПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

11.3035,Москва, Ж 35,lРаушская наб., д, 4/5

Филиал Illill "Патент", г, Ужгород, ул. Гагарина, 101