Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (i i) 48921 9 (61) Дополнительное к авт. свид-ву (22) ЗаЯвленО15.08.72 (21) 1828109/26-21 с присоедиисннеи заявки № (23) Приоритет

Опубликоваио 25. 10.75 Бюллетень № 39

Дата опубликования описания 23.01.76 (51) М, Кл.

Н 03 Ы 13/17

1 ааударствеиюй квинтет

Сваата Мвввстрвв СССР ав двлам взвбрвтвей я втарьпив (53) УДК 681.325

{088.8) (72) Авторы изобретения

В. H. Махов и Б, С. Новисов (71) 3 витель УРальский оРдена ТРУдового КРасного Знамен политехнически институт им. С. М. Кирова (54) АНАЛОГО-БИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение касается радиотехники и может использоваться для цепей спектрометрии ионизируюших излучений.

Известны 1аналого-цифровые преобразователи, содержашие источник эталонного напряжения, устройство управления источником эталонного напряжения, операционный усилитель, две ячейки памяти, блок управления, вентиль и блок синхронизации, причем выход источника эталонного напряжения соединен с первым входом устройства управления источником эталонного напряжения, второй вход которого подключен к выходу бдока синхронизации, а первый выход — к инвертируюшему входу операционного усилителя, первый вход вентиля соединен с входной клеммой, второй — с первым выходом блока, управления, а выход — с иеинвертируюшим входом операционного усилителя, первый и второй входы первой ячейки памяти соединены со вторым и третьим выходами устройства управления, первый и второй входы второй ячейки памятис четвертым и пятым выходами у".òðýéстьа управления, третьи входы обеих ячеек памяти соединены с выходом операционного усилителя, а их выходы - с

его неинвертирующим входом. Однако такой преобразователь не обеспечивае; кодирование сигналов обоих полярностей.

Бель изобретения — расширение функциональных воэможностей преобразоват— ля.

Йпя этого в него дополнительно введены делитель эталонного напряжения., дискриминатор знака входного сигнала, индикатор знака входного сигнала и преобразователь кода, причем выход источника эталонного напряжения соединен с первым входом делителя эталонного напряжения, второй вход которого подключен ко второму выходу устройства управления источником эталонного напряжения, а выход — к неиввертируюшему входу операционного усилителя, выход операционного усилителя, через дискриминатор знака входного сигнала соединен с третьим и четвертым входами устройства управпе.шя источником эта48 9219

lO

20 лонного напряжения и первым и вторым входами индикатора знака входного сигнала и преобразователя кодов, третьи входы которых соединены с выходом блока синхронизации, а первый и второй Вью>ды индикатора знака входного сигнала — с четвертым и пятым входами преобразователя кодов.

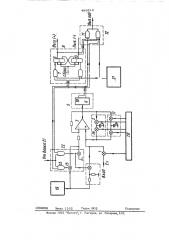

На чертеже дана блок»схема предлагаемого преобразователя.

Преобразователь содержит вентили

1 и 2, операционный усилитель 3, конденсатор 4, дискриминатор знака 5 с ггервым выходом 6, схему совпадения 7 индикатора знака 8, триггеры 9 и 10 индикатора знака 8, схему совпадения 11 преобразователя кода 12, схему совпаде-. ния 13, конденсатор 14, вентили 15-1 1, выход 18 дискриминатора знака 5, источник эталонного напряжения 19, устройство управления 2О, блок синхронизации 21, устройство управления эталоном 22, которое содержит схему совпадения 13.

Устройство работает следующим образом. В исходном состоянии аналого-цифрового преобразователя открыты вентили

1 и 2. Усилитель 3 работает в режиме повторителя и заряжает конденсатор 4 до величины Е, равной величине измеряемого сигналасЕ . Одновременно сигнал х пойается на вход дискриминатора знака 5.

Так как Е ) О, то дискриминатор знака х вырабатывает на своем выходе 6 сигнал управления, который через схему совпадения 7 индикатора знака 8 устанавливает триггер 9 в состояние Х .Сигнал с триггера 9 является сигналом индикации

"плюса" (положительной измеряемой величины). Сигнал со второго выхода триггера 9 блокирует триггер 10, и индикатор знака измеряемой величины остается в таком состоянии до окончания кодирования данного сигнала. Сигнал с триггера 9 также поступает на схему совпадения 1 1 преобразователя кода 2, что обеспечивает получение кода абсолютной величины измеряемого сигнала {Е ). Так х на выходе индикатора знака 8 получается сигнал; соответствуюший положительному значению измеряемой величины. Кроме того, сигнал управления дискриминатора эчака через схему совпадения 13 переводит преобразователь в режим вычитания эталона + Е2й из измеряемой величины.

При этом начинается процесс перезарядки конденсаторов 4 и 14 через усилитель

3;при этом вентили 15-17 открыты, остальные — закрыты. Конденсатор 14 заряжается до величины Š— 2/Е - Еур

Эта величина также подается на вход дискриминатора знака. В случае, если полученная величина положительна„ на выходе 6 дискриминатора знака 5 вырабатывается сигнал управления, который через схему совпадения 1 1 подается на выход преобразователя кода и соответствует состоянию. Х и первом разряде кода измеряемого сигнала.

При этом преобразователь остается в прежнем режиме. Если полученная величина отрицательна, то на выходе 18 дискриминатора знака 5 появляется сигнал, который переводит преобразователь в режим сложения эталона Ññ измеряемой величиной.

На выходе преобразователя кода сигнал отсутствует, что дает состояние О" в соответствующем разряде кода измеряемого сигнала. Далее процесс повторяется до тех пор, пока величина Ео не сменит свой знак. В этом случае преобразователь снова переходит в предыдущий режим.

Предмет изобретений

А нал ого-ц ифровой преобраэовател ь, содержаший источник эталбиного напряжения, устройство управления источником эталонного напряжения, операционный усилитель, две ячейки памяти, блок управления, вентиль и блок синхронизации, i,ðèчем выход источника эталонного напряжения соединен с первым входом устройства управления источником эталонного напряжения, второй вход которого подключен к выходу блока синхронизации, а первый выход - к инвертируюшему входу операционного усилителя, первый вход вентиля соединен с входной клеммой, второй — с первым выходом блока управления, а выходс неинвертируюшим входом операционного усилителя, первый и второй входы первой ячейки памятисоединенысо вторым и третьим выходами устройства управления, первый и второй входы второй ячейки памяти - е четвертым и пятым выходами устройства управления, третьи входы обеих ячеек памяти соединены с выходо, операционного усилителя, а их выходы— с его неинвертируюшим входом, о т л ич а ю ш и и с я тем, что, с целью расширения функциональных воэможностей преобразователя, в него дополнительно введены делитель эталонного напряжения, дискриминатор знака входного сигнала и индикатор знака входного сигнала и поеобраэователь кода, причем выход источника эталонного напряжения соединен с первым входом делителя эталонного напря489219 жения, второй вход которого подключен ко второму выходу устройства управления источником эталонного напряжения, а выход к неинвертируюшему входу операционного усилителя, выход операционного усилителя через дискриминатор знака входного сигнала соединен с третьим и четвертым входами устройства управления источником эталонного напряжения и первым и вторым входами индикатора знака входного сигнала и преобразователя кодов, трен.,и входы которых соединены с выходом блока синхронизации, а первый и второй Bbl» ходы индикатора знака входного сигцлпа с четвертым и пятым входами преобразователя кодов.