Устройство для сжатия многоканальных аналого-дискретных данных

Иллюстрации

Показать всеРеферат

5I

1 (») 489235

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено20.03.73 (21) 1896607!26-9 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.10.75,Бюллетень № 39 (4Б) Дата опубликования описания 03.02.76 (51) М. Кл.H 04j 7/00

Государственный комитат

Саввтв Министров СССР по делам нзоаретений и открытий (Я) УДК621.398.. 8 (088. 8) (72) Автор изобретения

В. А. Свириденко (54) УСТРОЙСТВО ДЛЯ СЖАТИЯ

МНОГОКАНАЛЬНЫХ АНАЛОГОВО-ДИСКРЕТНЫХ ДАННЫХ преобразователя, а управляющие входы дискретизатора, генератора ортогональных функций, одномерного ортогональногопреобразова- теля, адресного блока и буферного запоминаю-1 щего блока подключены к соответствующим выходам управляющего блока.

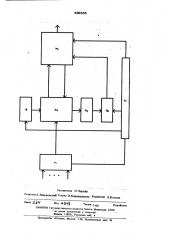

На чертеже приведена структурная электрическая схема устройства.

Устройство для сжатия многоканальных аналогово-дискретных данных содержит последовательно соединенные дискретизатор 1, число входов которого соответствует числу компонентов Я (t) многоканального сообщения, одномерный ортогональный преобразователь 2 и буферный запоминающий блок 3.

Второй вход преобразователя 2 соединен с выходом генератора 4 ортогональных функций, а второй выход преобразователя 2 через последовательно соединенные пороговый блок 5 и адресный блок 6 подключен к второму входу буферного запоминающего блока

3, дополнительный выход которого подключен к третьему входу преобразователя 2, а выход является выхрдом устройства.

Управляющие входы дискретизатора 1, j

Изобретение относится к телемеханике.

Известно устройство для сжатия многоканальных анологово-дискретных данных, содержащее последовательно соединенные дис кретиза тор, одномерный ортогональный 1 преобразователь и буферный запоминающий блок, причем к второму входу одномерного ортогонального преобразователя подключен, выход генератора ортогональных функций.

Однако известное устройство не сокра- 1р

° щает значительную долю информационной избыточности в исходном двумерном массиве данных, обусловленной авто- и взаимокорреляционными связями внутри него.

Целью изобретения является сокращение 15 избыточности, обусловленной авто- и взаимокорреляционными связями внутри исходного двумерного массива данных.

Для этого дополнительный выход одномерного ортогонального преобразователя че-: 20 рез последовательно соединенные пороговый блок и адресный блок подключен к второму входу буферног о запоминающего блока, дополнительный выход которого подключен к третьему входу одномерного ортогонального 25 (71) Заявитель Московский ордена Трудового Красного Знамени электротехнический институт связи

489235 генератора 4 ортогональных функций, преобразавателя 2, адресного блока 6 и буфер,ного запоминающего блока 3 подключены к управляющему блоку 7, обеспечивающему синхронизацию работы устройства.

Устройство работает следующим образом.

Подаваемые на вход дискретизатора 1 компоненты rn, (Ц g -мерного сообщения

m(t) считываются в одни и те же моменты времени (параллельное считывание) . через интервал дискретизации 4t . Далее вектор ц ), где К=О, 1, 2, ... поступают в преобразователь 2, где подвергается преобразованию с N > N -размерной матрицей P столбцы которой представляют собой ь ортогональные векторы p вырабатыI ваемые в генераторе 4 ортогональных функций. Результат этого преобразования, которое совершается за время Ь /2, вектор

-ь Ф

1 у = P щ записывается в буферныи запоминающий блок 3. За оставшуюся часть времени Ь1 12 до нового момента считывания с буферного запоминающего блока 3 с блска 7 управления подается сигнал на выдачу в блок 2 одной из строк матрицы полученной на предыдущем интервале обработки длинной в Т= N

Преобразованный вектор у проходит через пороговый блок 5, где происходит отбор высокоинформативных его компонент, превосходящих по величине установленный порог, . и далее через блок адресации

6, где на них накладывается "адресный признак, или его снабжают "адресным" сиг- налом, позволяющим дешифрировать преобразованный вектор-строку. Через интервал

М описанная операция повторяется: с п тывается pl()) в дискретизаторе 1 и нодается на блок 2, гд» вектор-столбец ф + ) д ) ) преобразовывается в вектор М и затем поступает в буферный

М 1 запоминающий блок 3.

Вектор-строки матрицы (извлекаются из буферного запоминающего блока 3 через интервал кратный Т, и преобразовыФ ваются за время g$ /2 в вектор

Число ненулевых компонент вектора Z меньше в среднем, чем Ч в g раз, где g — коэффициент сжатия по выборкам.

Ь

Поэтол у если длина в двоичных единицах ф вектора, ° и сопровождающей его слу1 жебной (адресной) информации меньше, чем вектора-cxpoKn, извлеченной из буфер4 ного запоминающего блока 3, то на последующем этапе (преобразовании следующе- 1

ro вектора . ) информация о векто« i+( ре 2; . записывается сразу же за векто-, р+1 ром g .. Такая передача позволит по

1 адресным признакам восстановить исходное сообщение.

Емкость буферн. го запоминающего блока 3 в двоичных единицах должна быть

1О рассчитана так, чтобы в моменты актив ности, когда все компоненты векторов

-Ф информативны, учитывать дополнитель-, ное присутствие служебных слов. Значит

15 при записи вектора необходимо запи-!

l сать все его компоненты и оставить пустыми ячейки для адресной информации. Такой выбор емкости буферного запоминающего блока 3 позволяет избежать его переполне1 ния и потерь данных. В ином случае в моменты активности источника возможны потери, которые целесообразно допустить за счет компонентов вектора с минималь- .

i» ной величиной (или амплитудой при аналоговой обработке).

Формула изобретения

Устрой гво для сжатия многоканальных

30, аналогово-дискретных данных, содержащее ! последовательно соединенные дискретизатор, одномерный ортогональный преобразователь и буферный запоминающий блок, причем к второму входу одномерного ортогонального

®5 преобразователя подключен выход генератора ортогональных функций, о т л и ч а ющ е е с я тем, что, с целью сокращения избыточности, обусловленной авто- и взаимокорреляционными связями внутри исходf 1

4> ного двумерного массива данных, дополнительный выход одномерного ортогонального преобразователя через последовательно соединенные пороговый блок и адресный блок подключен к второму входу буферного запоминающего блока, дополнительный выход которого подключен к третьему входу одномерного ортогонального преобразователя, а управляющие входы дискретизатора, гене)оратора ортогональных функций, одномерного ортогонального преобразователя, адресного блока и буферного запоминающего блока подключены к соответствующим ebtходам управляющего блока.

48923S

Заказ, Я4/

Иад. J4))g(Тираж 7 О

Подвойское

ЦНИИПИ Гесударственыого комитета Совета Министров СССР по делам изобретений и открытий

Москва, 1И035, Раушская наб., 4

Предприятие Патент>, Москва, Г-59, Бережковская наб., 24

Составитель И.Яорщщ

Редактор A. Зиньковский Техред И К Раидащовв КорректоР Л.Ко