Устройство для декодирования избыточных кодов

Иллюстрации

Показать всеРеферат

СПИ

ИЗОБ (») 489239

Союз Советских

Социалистических

Республик

К АВТОРСКО (61) Дополнительно (22) Заявленс06. 12 с присоединением (23) Приоритет (43) Опубликоваио2 (45) Дата опублик (51) М. Кл.Н 04t 1/10

Н 03к 13/32

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.394.. 1 4 (088.8 ) (72) Автор изобретения

Ю. Ф. Рычков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ИЗБЫТОЧНЫХ

КОДОВ

Изобретение относится к передачи циф-" ровых сообщений каналам связи, в частности к устройствам помеховащитного коди-. рования.

Известно устройство для декодирования избыточных кодов, содержащее последовательно соединенные детектор и буферный накопитель, выход которого через схему

НЕ" подключен к одному из входов сум матора, другой вход которого соединен с выходом генератора контрольных сигналов, а выход его — со входом решающего блока.

Между выходом генератора контрольных сигналов и выходом решающего блока включена выходная схема "И".

Однако в известном устройстве происхо-, дит предварительное выравнивание единичных элементов сигнала, что снижает общую помехоустойчивость приема, так как при преобразовании сигнала теряется часть содержащейся в нем информации.

Цель изобретения — повышение помехоустойчивости приема информации при межсимвольных помехах.

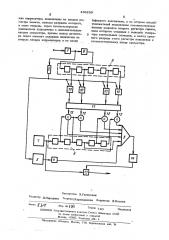

Это достигается тем, что выход детектора через анализатор полярности сигнала подключен ко входу первого регистра, выходы разрядов которого через соответствую5 . щие корреляторы подключены ко входам регистра памяти, выходы разрядов которого, в свою очередь, через соответствующие умножители подключены к дополнительным входам сумматора. Выход детектора через элемент задержки подключен ко вторым входам корреляторов и ко входу буферного накопителя, а ко вторым входам умножителей подключены соответствующие,, выходы разрядов второго регистра сдвига, вход которого соединен с выходом генератора контрольных сигналов, а выход среднего разряда этого регистра подключен к соответствующему входу сумматора, На чертеже представлена функциональная схема предлагаемого устройства для декодирования избыточных кодов.

Устройство содержит детектор 1, соединенный своим выходом через элемент задержки 2 со входом, буферного накопителя 3, выход которого через схему НЕ

489239

4 подключен к одному из входов суммато- ра 5. К другому входу сумматора подклю- . чен выход среднего разряда, регистра сдвига 6, вход которого соединен с выхоI дом генератора 7 контрольных сигналов.

Между детектором 1 и дополнительными входами сумматора 5 включена схема отработки эхо-сигналов, содержащая анализатор 8 полярности сигнала,i соединенный своим входом с детектором, а выходом — со входом Регистра 9, выходы разрядов которого через соответствующие корреляторы 10 подключены ко входам регистра памяти 11, выходы разрядов которого, в свою очередь, через соответст- . вующие умножители 12 подключены к дополнительным входам сумматора 5. Вто, рые входы корреляторов 10 соединены с выходом элемента задержки 2, а вторые входы умножителей 12 — с выходами соответствующих разрядов регистра сдвига 6.

Выход генератора контрольных сигналов соединен с выходной схемой «И 13, к

,управляющему входу которой подключен решающий блок 14, соединенный своим входом с выходом сумматора 5.

Описываемое устройство работает следующим образом. Поступающие из канала связи сигналы детектируются детектором

1 и через элемент задержки 2 записываются в буферный накопитель 3, откуда они считываются и через схему "HE" 4 подаются на один из входов сумматора 5.

Генератор 7 генерирует контрольный сигнал, соответствующий одному из допустимых для передачи сигналов. Контрольный сигнал через регистр сдвига 6 поступает на соответствующий вход сумматора 5.

Сумматор 5 вычисляет разницу между единичными элементами контрольного сигнала и сигнала, поступающего из буферного накопителя 3. Решающий блок 14 анализирует эти разницы на всем протяжении сигнала и выбирает контрольный сигнал, наиболее близко совпадающий с принятым из канала связи. Этот сигнал через выходную схему "И" 13, управляемую решающим блоком 1, поступает на выход устройства.

При наличии межсимвольных помех впереди и позади передаваемого по каналу связи импульса появляются эхо-сигналы, которые накладываются на соседние импульсы. В этом случае для повышения исправляющей способности избыточного кода, необходимо форму контрольного сигнала привести в соответствие с формой сигнала, принятого из канала связи, т. е. наложить

40, на каждый его единичный. элемент эхо-сигналы от соседних, единичных элементов.

Для этого сигналы с выхода детектора 1 подаются на анализатор 8 полярности сигнала, который определяет полярность каждого единичного элемента сигнала и записывает соответствующую метку (+, единица, — единица) в регистр 9.

С каждым отсчетом метки продвигаются по -Регистру 9,. а новая метка записывается в левый разряд. Параметры элемен,та задержки 2 выбраны так, что при появ лении единичного элемента сигнала на его .выходе соответствующая ему метка полярности находится в среднем разряде регистра 9. Среднее значение эхо-сигналов отрабатывается путем корреляции единичного элемента сигнала в корреляторах 10 с полярностями соседних элементов. Значения эхо-сигналов, отрабатываемые корреляторами 10, записываются в регистр памяти

11 и с его разрядных выходов подаются на соответствующие умножители 12.

На другие входы умножителей 12 подаются сигналы с соответствующих разрядов регистра 6, пропорциональные единичным элементам контрольногс сигнала, находящимся справа и слева от обрабатываемоI

ro элемента, снимаемого с среднего разряда регистра 6 на сумматор 5.

Выходные напряжения умножителей 12 в каждый момент времени пропорциональны эхо-сигналам, действующим на обрабатываемый элемент контрольного сигнала.

Эти сигналы поступают на дополнительные входы сумматора 5 одновременно с обрабатываемым элементом контрольного сигнала, снимаемым со среднего разряда регистра 6, и накладываются на него.

Предмет изобретения

Устройство для декодирования избыточных кодов, содержащее последовательно соединенные детекторы и буферный накопитель, выход которого через схему "НЕ подключен к одному из .входов сумматора, другой вход которого соединен с выходом генератора контрольных сигналов, а выход его - со входом решающего блока, причем между выходом генератора контрольных сигналов и выходом решающего блока включена выходная схема "И", о т л и ч а ю . ш е е с я тем, что, с целью повышения помехоустойчивости приема информации при межсимвольных помехах, выход детектора через анализатор полярности сигнала подключен ко входу первого регистра, выходы разрядов которого через соответствую1

489239

Составитель 9.Гилянская

Л.народная 1 е" ред И.Карандашова Корректор тт Ко

Заказ ", Изд. р6 ((ф Тираж 740 Подписное

ЦИИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24 щие корреляторы подключены ко входам регистра памяти, выходы разрядов которого, в свою очередь, через соответствующие умножители подключены к дополнительным входам сумматора, причем выход детектора через элемент задержки подключен ко вторым входам корреляторов и- ко входу

6 буферного накопителя, а ко вторым входам умножителей подключены соответствующие выходы разрядов второго регистра сдвига, вход которого соединен с выходбм генератора контрольных сигналов, а выход среднего разряда этого регистра подключен к соответствующему входу сумматора.