Устройство для тактовой синхронизации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (1 1) 489242

Союз Советских

Социалистиыеских

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 14.09.73 (21) 1958713/26-9 с присоединением заявки №(23) Приоритет (43) Опубликовано 25,10.75 Бюллетень № 39 (45) Дата опубликования описания 08.01.76 (51) М. Кл.

Н 041 7/02

Н ОЗЬ 3/04

Государственный комитет

Совета Министров СССР оо делам изобретений н открытий (53) УДК 621.394, .662.2:621 394 (088,8) Д Г Нисневич и А Б Бучацкий (72) Авторы изобретения (71} Заявитель (54) УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к передаче дать» ных и к системам автоматического управле, ния.

Известно устройство для тактовой синх ронизации, содержащее последовательно соединенные управляемый делитель, дешифратор,:эл еме нт И ЛИ а также фазовый детектор, подключенный к источнику сигнала тактовой частоты и выходу элемента ИЛИ, являющемуся выходом устройства. 10

Однако известное устройство не обеспе» чивает автоматическую работу при смене рабочих частот.

Целью изобретения является расширение диапазона рабочих частот. 15

Для этого параллельно входам фазового детекторы подключены входы частотного дискриминатора, весовой выход которого через решающий узел подключен к кодовому.компаратору; вторым входом соединен- QQ ному с выходом управляемого делителя, а выходом - с блоком для сопряжения, второй вход которого соединен с источником опорного сигнала, а выходы — со счетным и установочным входами управляемого де- 26 лителя, а пороговые выходы частотного дискриминатора и фазового детектора через элемент совпадения и второй решающий узел, подключенный к весовому выходу фазового детектора подсоединены к управляющему входу дешифратора.

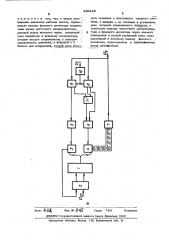

На чертеже приведена структурная электрическая схема устройства.

Устройство для тактовой синхронизации содержит управляемый делитель 1, счетный и установочный входы которого соединены с местным источником опорных сигналов через блок для сопряжения 2.

Выходные цепи всех разрядов управляемого делителя 1 подключены к рабочим входам кОдОвОгО ко мпаратора 3 и деш ифратора 4. Управляющий вход кодового компа« ратора 3 соединен с выходом первого ре . шающего узла 5, управляющий вход де шифратора 4 соединен с вторым решающим узлом 6 ° Выход кодового компаратора

3 соединен с управляющим входом блока для сопряжения 2, а выходы дешифратора 4 - с входами логического элемента

ИЛИ 7. Выход элемента ИЛИ 7 подклю489242

3 чен к объединенным первым входам фа ) зового детектора 8 и частотного дискри. минатора 9 и является общим выходом; устройства (U> ).

Объединенные вторые входы фазового детектора 8 и частотного дискриминатора . 9 соединены с выходом источника такто, вой частоты 10, вход которого подключен

-к источнику входных сигналов ц

Пороговые выходы частотного дискриминатора 9 и фазового детектора 8 соедине

2 ны с инверсным и прямым входами логического элемента И 11 соответственно, вы-ч

7 ход которого подключен к коммутационно- му входу второго решающего узла 6, ве- ,совой вход которого соединен с рабочим выходом фазового детектора 8. Рабочий выход частотного дискриминатора 9 соеди . нен с весовым входом первого решающего узла 5.

Устройство работает следующим обра зом.

При изменении номинала частоты сигн ла Q или отклонения ее значения от с номинала на величину, выше допустимой, на выходах .,фазового детектора 8 и ча-,: стотного дискриминатора 9 появятся сит палы рассогласования. Далее работа уст ройства разбита на два этапа.

На первом этапе сигйал с порогового выхода частотного дискриминатора 9 чей рез логический элемент И 1 1 воздействует на коммутационный вход второ

ro решающего узла 6, запрещая работу последнего. Одновременно по сигналу с весового выхода частстного дискриминатора 9 первый решающий узел 5 выраба

1 тывает код - уставку коэффициента делений, соответствующую расхождению по частоте сигналов U H U

Êon-уставка;. подается на кодовый комнаратор 3, с выхода которого снима ется сигнал, воздействующий на блок для сопряжения 2 таким образом, что управляемьМ делитель 1 по входу устанавлнва ется в исходное состояние после отсчета заданного количества импульсов. Тем са-1 мым осуществляетса деление частоты r нератора опорных сигналов Q на тре

on 1 буемое число.

После установления переходных npotцессов частоты сигналов U и U выт равнн аются щЧезают сигналы на выхо подключенный к источнику сигнала такто-;

1вой частоты и выходу элемента ИЛИ, аь 60 д4ющемуся выходом устройства, о т л идах Частотного дискриминатора 9, на выходе элемента .. И 11 вырабатывается сигнал, включающий второй решающий узел 6. Начинаетса второй этап подстройки е

Сигнал с фазового детектора 8 по весовому выходу воздействует на

:. второй решающий узел 6, В последнем вырабатывается код, поступающий на вход дешифратора 4. При этом на вхсь» ды всех элементов совпадения дешифратор

4, кроме одного, фаза сигнала которого соответствует требуемой, поступает команда "Запрет, Благодаря этому при каж+ у дом цикле работы дешифратора 4 возбуж

: дается только один элемент .-,совпадения,который и вырабатывает выходной сигнал.

Последний через элемент ИЛИ 7 поступает на выход устройства.

Предложенное устройство тактовой синх

I ронизации астатичное как по частоте, так и по фазе, Это позволяет обеспечить вы сокое качество регулировании и осуществлять подстройку сигнала с точностью до фазы. Последнее качество имеет особое значение для импульсных систем связи с временным разделением каналов.

Для обеспечении четкого разделения во времени двух этапов работы необходимо, чтобы частотный дискриминатор 9 при появ ленин ошибки практически мгновенно выраба ( тывал сигнал на своем пороговом выходе, Сигнал на весовом выходе -настиного ди- ! скриминатора 9 является результатом ря- да повторных измерений и вырабатывается с задержкой относительно сигнала на пороговом выходе.

Выполнение указанного условия иск лючает возможность воздействия на си стему биений на выходе фазового детектора 8 на первом этапе настройки.

Последнее благоприятно сказывается на характере переходного процесса в сиотем4, 1

При малых расхождениях частот сигнал лов Q и 0 не выходящих за пределы т С зоны нечувствительности частотного диск риминатора 9, набегающая ошибка по фазе будет периодически компенсироваться кон туром: фазовый детектор 8 - второй ре» шающий узел 6 - дешифратор 4. При этом периоды компенсации будут опреде лятьса зоной нечувствительности фазового .детектора 8 и моментом появления сит ,нала на его пороговом выходе.

Формула изобретения

Устройство для тактовой синхронизации, i содержащее последовательно соединенные,, управляемый делитель, дешифратор, эле- мент ИЛИ, а также фазовый детектор, 489242

Ивд. И (1 ф Тираж 740 Подписное

Заказ ф,Я

ЦНИИПИ Государствеииото комитета Совета Министров СССР

Предприятие «Патент>, Москва, Г-59, Бережковская наб., 24 ч а ю щ е е с я тем, что, с пелью рас-

I ширения диапазона рабочих частот, парал-; лельно входам фазового детектора подключены входы частотного дискриминатора; весовой выход которого через решающий узел подключен к кодовому компаратору, вторым входом соединенному с выходом управляемого делителя, а выходом - с блоком для сопряжения, второй вход кото

L рого соединен с источником опорного сигънала, а выходы - со счетным и установочным входами управляемого деятеля, а пороговые выходы частотного дискримина- тора и фазового детектора через элемент совпадения и второй решающий узел, под ключенный к весовому выходу фазового < детектора, подсоединены к управляющему входу дешифратора.